Intel® Server Board SE7320SP2 & Intel Server Board SE7525GP2 TPS Functional Architecture

Revision 2.0

66

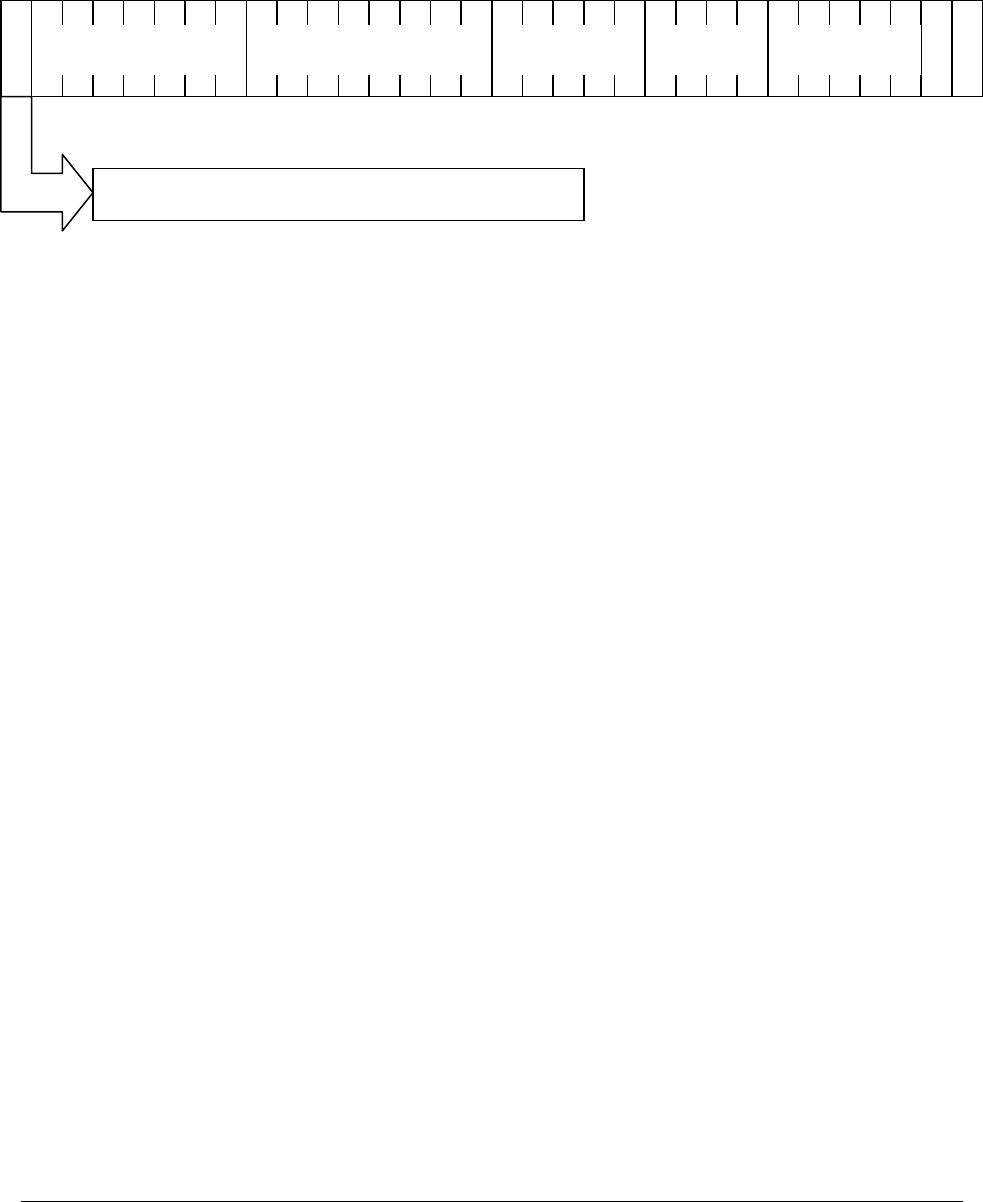

3.7.3.1 CONFIG_ADDRESS Register

CONFIG_ADDRESS is 32 bits wide and contains the field format shown in the following figure.

Bits [23::16] choose a specific bus in the system. Bits [15::11] choose a specific device on the

selected bus. Bits [10:8] choose a specific function in a multi-function device. Bit [8::2] select a

specific register in the configuration space of the selected device or function on the bus.

Figure 12 - CONFIG_ADDRES Register

3.7.3.1.1 Bus Number

PCI configuration space protocol requires that all PCI buses in a system be assigned a Bus

Number, Furthermore, bus numbers must be assigned in ascending order within hierarchical

buses. Each PCI bridge has registers containing its PCI Bus Number and subordinate PCI Bus

Number, which must be loaded by POST code. The Subordinate PCI Bus Number is the bus

number of the last hierarchical PCI bus under the current bridge. The PCI Bus Number and the

Subordinate PCI Bus Number are the same in the last hierarchical bridge.

3.7.3.1.2 Device Number and IDSEL Mapping

Each device under a PCI bridge has its IDSEL input connected to one bit out of the PCI bus

address/data signals AD[31::11] for the PCI bus. Each IDSEL-mapped AD bit acts as a chip

select for each device on PCI. The host bridge responds to a unique PCI device ID value, that

along with the bus number, cause the assertion of IDSEL for a particular device during

configuration cycles. The following table shows the correspondence between IDSEL values and

PCI device numbers for the PCI bus. The lower 5-bits of the device number are used in

CONFIG_ADDRESS bits [15::11].

00

Register

017 810 11 15 16 23 24 30 31

Function Device Bus Number Reserved

Enable bit (‘1’ = enabled, ‘0’ = disabled)