Rev.2.00 Nov 28, 2005 page 13 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 1. Overview

Under development

This document is under development and its contents are subject to change.

1.6 Pin Description

Tables 1.9 to 1.11 list the pin descriptions.

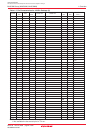

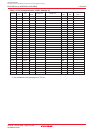

Table 1.9 Pin Description (100-pin and 128-pin Versions) (1)

I

I

I

I

I

I/O

I/O

O

I/O

I/O

O

O

O

I

O

I

VCC1, VCC2,

VSS

AVCC, AVSS

_____________

RESET

CNVSS

BYTE

D0 to D7

D8 to D15

A0 to A19

A0/D0 to A7/D7

A1/D0 to A8/D7

_______ _______

CS0 to CS3

_________ ______

WRL/WR

_________ ________

WRH/BHE

______

RD

ALE

__________

HOLD

__________

HLDA

________

RDY

Power supply

input

Analog power

supply input

Reset input

CNVSS

(2)

External data

bus width

select input

(2)

Bus control

pins

(3)

Apply 3.0 to 5.5V to the VCC1 and VCC2 pins and 0V to the VSS

pin. The VCC apply condition is that VCC2 = VCC1

(1)

.

Applies the power supply for the A/D converter. Connect the AVCC

pin to VCC1. Connect the AVSS pin to VSS.

The microcomputer is in a reset state when applying “L” to the this pin.

Switches processor mode. Connect this pin to VSS to when after

a reset to start up in single-chip mode. Connect this pin to VCC1

to start up in microprocessor mode.

Switches the data bus in external memory space. The data bus

is 16-bit long when the this pin is held “L” and 8-bit long when

the this pin is held “H”. Set it to either one. Connect this pin to

VSS when an single-chip mode.

Inputs and outputs data (D0 to D7) when these pins are set as

the separate bus.

Inputs and outputs data (D8 to D15) when external 16-bit data

bus is set as the separate bus.

Output address bits (A0 to A19).

Input and output data (D0 to D7) and output address bits (A0 to

A7) by time-sharing when external 8-bit data bus are set as the

multiplexed bus.

Input and output data (D0 to D7) and output address bits (A1 to

A8) by time-sharing when external 16-bit data bus are set as the

multiplexed bus.

_______ _______ _______ _______

Output CS0 to CS3 signals. CS0 to CS3 are chip-select signals

to specify an external space.

________ _________ ______ ________ _____ ________ _________

Output WRL, WRH, (WR, BHE), RD signals. WRL and WRH or

________ ______

BHE and WR can be switched by program.

________ _________ _____

• WRL, WRH and RD are selected

________

The WRL signal becomes “L” by writing data to an even address

in an external memory space.

_________

The WRH signal becomes “L” by writing data to an odd address

in an external memory space.

_____

The RD pin signal becomes “L” by reading data in an external

memory space.

______ ________ _____

• WR, BHE and RD are selected

______

The WR signal becomes “L” by writing data in an external

memory space.

_____

The RD signal becomes “L” by reading data in an external

memory space.

________

The BHE signal becomes “L” by accessing an odd address.

______ ________ _____

Select WR, BHE and RD for an external 8-bit data bus.

ALE is a signal to latch the address.

__________

While the HOLD pin is held “L”, the microcomputer is placed in

a hold state.

__________

In a hold state, HLDA outputs a “L” signal.

________

While applying a “L” signal to the RDY pin, the microcomputer

is placed in a wait state.

Signal Name Pin Name I/O Type Description

I: Input O: Output I/O: Input/Output

NOTES:

1. In this manual, hereafter, VCC refers to VCC1 unless otherwise noted.

2. Connect to VSS in T/V-ver..

3. Not available the bus control pins in T/V-ver..