Rev.2.00 Nov 28, 2005 page 319 of 378

REJ09B0124-0200

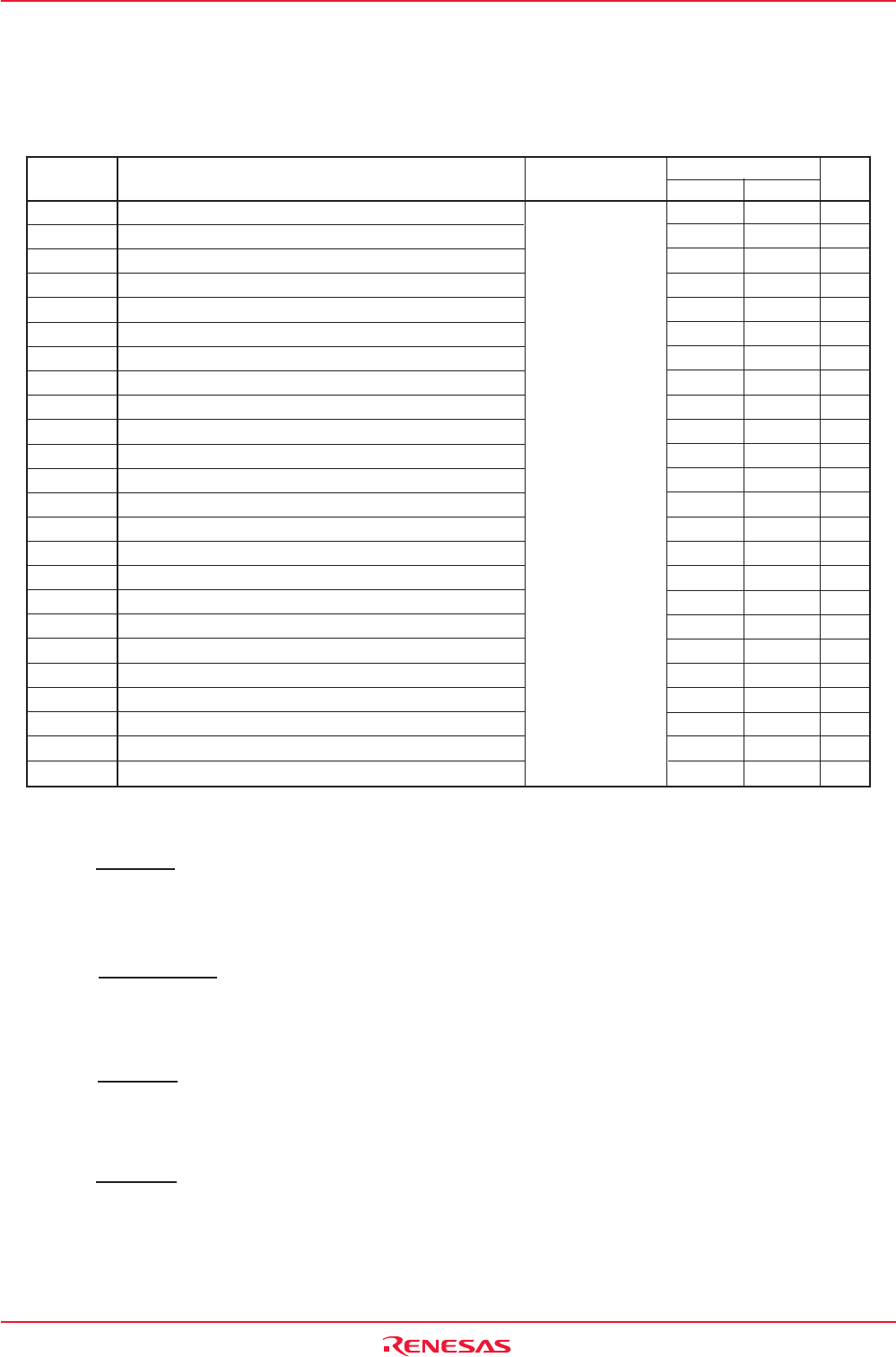

M16C/6N Group (M16C/6NK, M16C/6NM) 22. Electric Characteristics (Normal-ver.)

Under development

This document is under development and its contents are subject to change.

4

(NOTE 1)

(NOTE 1)

4

(NOTE 1)

(NOTE 1)

0

0

4

(NOTE 2)

(NOTE 1)

–4

(NOTE 3)

(NOTE 4)

0

0

td(BCLK-AD)

th(BCLK-AD)

th(RD-AD)

th(WR-AD)

td(BCLK-CS)

th(BCLK-CS)

th(RD-CS)

th(WR-CS)

td(BCLK-RD)

th(BCLK-RD)

td(BCLK-WR)

th(BCLK-WR)

td(BCLK-DB)

th(BCLK-DB)

td(DB-WR)

th(WR-DB)

td(BCLK-HLDA)

td(BCLK-ALE)

th(BCLK-ALE)

td(AD-ALE)

th(ALE-AD)

td(AD-RD)

td(AD-WR)

tdZ(RD-AD)

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Address output delay time

Address output hold time (refers to BCLK)

Address output hold time (refers to RD)

Address output hold time (refers to WR)

Chip select output delay time

Chip select output hold time (refers to BCLK)

Chip select output hold time (refers to RD)

Chip select output hold time (refers to WR)

RD signal output delay time

RD signal output hold time

WR signal output delay time

WR signal output hold time

Data output delay time (refers to BCLK)

Data output hold time (refers to BCLK)

Data output delay time (refers to WR)

Data output hold time (refers to WR)

__________

HLDA output delay time

ALE signal output delay time (refers to BCLK)

ALE signal output hold time (refers to BCLK)

ALE signal output delay time (refers to Address)

ALE signal output hold time (refers to Address)

RD signal output delay from the end of Address

WR signal output delay from the end of Address

Address output floating start time

Symbol

Parameter

Min.

Standard

Unit

Max.

Switching Characteristics

(Referenced to VCC = 3.3V, VSS = 0 V, at Topr = –40 to 85 °C unless otherwise specified)

Table 22.45 Memory Expansion Mode and Microprocessor Mode

(for 2- to 3-wait setting, external area access and multiplexed bus selection)

50

50

40

40

50

40

25

8

Measuring

condition

Figure 22.12

NOTES:

1. Calculated according to the BCLK frequency as follows:

0.5 ✕ 10

9

f(BCLK)

– 10 [ns]

2. Calculated according to the BCLK frequency as follows:

(n –0.5) ✕ 10

9

f(BCLK)

– 50 [ns] n is “2” for 2-wait setting, “3” for 3-wait setting.

3. Calculated according to the BCLK frequency as follows:

0.5 ✕ 10

9

f(BCLK)

– 40 [ns]

4. Calculated according to the BCLK frequency as follows:

0.5 ✕ 10

9

f(BCLK)

– 15 [ns]

VCC = 3.3V