Rev.2.00 Nov 28, 2005 page 51 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 7. Bus

Under development

This document is under development and its contents are subject to change.

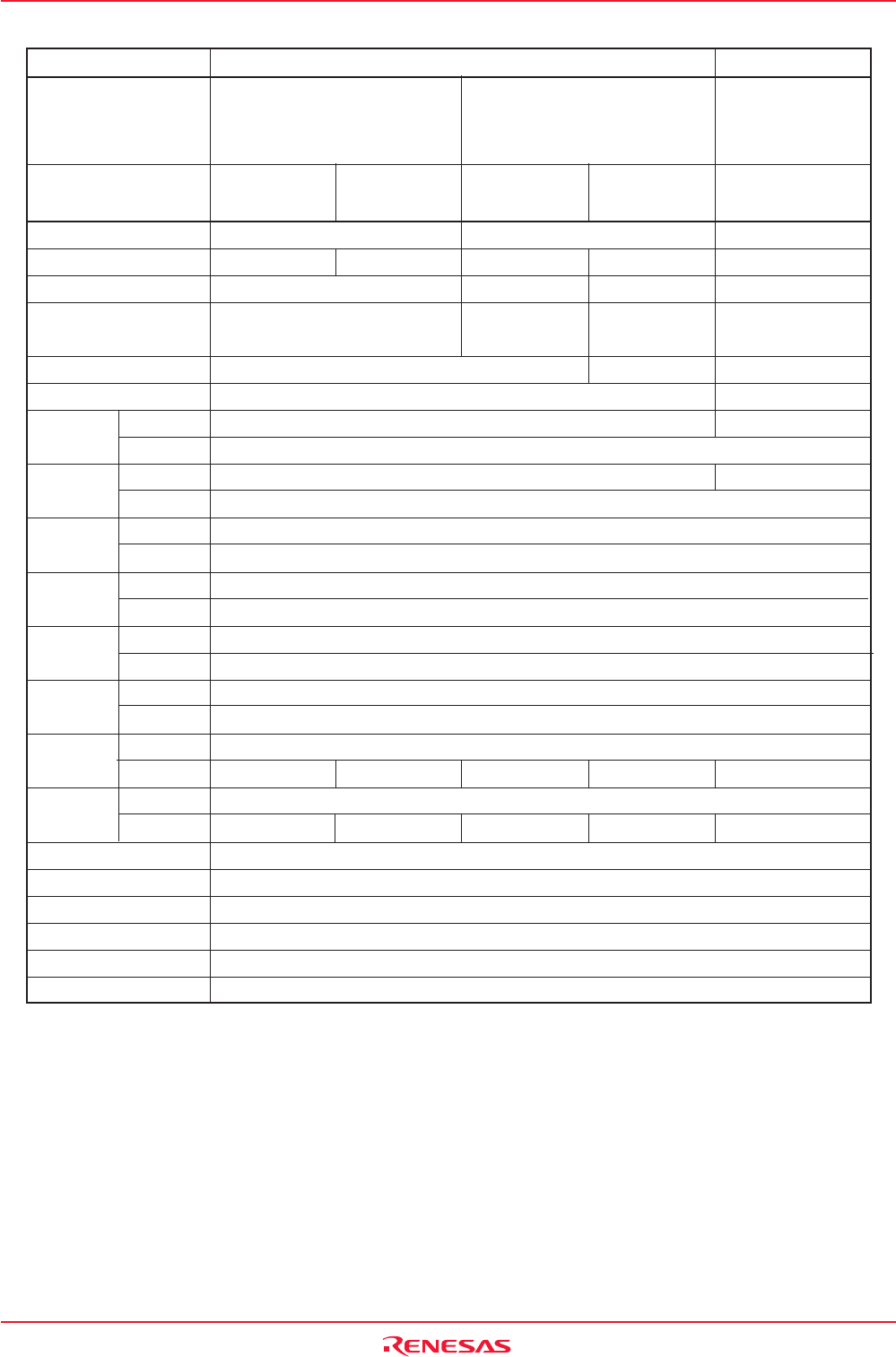

Table 7.6 Pin Functions for Each Processor Mode

Processor Mode Memory Expansion Mode or Microprocessor Mode

Memory Expansion Mode

PM05 to PM04 Bits 00b (separate bus)

_______

01b (CS2 is for multiplexed bus and

11b

others are for separate bus)

(multiplexed bus

for

_______

10b (CS1 is for multiplexed bus and

the entire space)

(1)

others are for separate bus)

Data Bus Width 8 bits 16 bits 8 bits 16 bits 8 bits

BYTE Pin “H”“L”“H”“L” “H”

P0_0 to P0_7 D0 to D7 D0 to D7

(4)

I/O ports

P1_0 to P1_7 I/O ports D8 to D15 I/O ports

D8 to D15

(4)

I/O ports

P2_0 A0 A0/D0

(2)

A0 A0/D0

P2_1 to P2_7 A1 to A7 A1 to A7 A1 to A7

A1 to A7/D1 to D7

/D1 to D7

(2)

/D0 to D6

(2)

P3_0 A8 A8/D7

(2)

A8

P3_1 to P3_3 A9 to A11 I/O ports

P3_4 PM11 = 0 A12 to A15 I/O ports

to P3_7 PM11 = 1 I/O ports

P4_0 PM06 = 0 A16 to A19 I/O ports

to P4_3 PM06 = 1 I/O ports

P4_4 CS0 = 0 I/O ports

CS0 = 1

_______

CS0

P4_5 CS1 = 0 I/O ports

CS1 = 1

_______

CS1

P4_6 CS2 = 0 I/O ports

CS2 = 1

_______

CS2

P4_7 CS3 = 0 I/O ports

CS3 = 1

_______

CS3

P5_0 PM02 = 0

_______

WR

PM02 = 1

-

(3)

________

WRL

-

(3)

________

WRL

-

(3)

P5_1 PM02 = 0

________

BHE

PM02 = 1

-

(3)

_________

WRH

-

(3)

_________

WRH

-

(3)

P5_2

_____

RD

P5_3 BCLK

P5_4

__________

HLDA

P5_5

__________

HOLD

P5_6 ALE

P5_7

________

RDY

I/O ports: Function as I/O ports or peripheral function I/O pins.

NOTES:

1. For setting the PM01 to PM00 bits to “01b” (memory expansion mode) and the PM05 to PM04 bits to

_____

“11b” (multiplexed bus assigned to the entire CS space), apply “H” to the BYTE pin (external data bus is

an 8-bit width). While the CNVSS pin is held “H” (VCC), do not rewrite the PM05 to PM04 bits to “11b”

after reset. If the PM05 to PM04 bits are set to “11b” during memory expansion mode, P3_1 to P3_7

_____

and P4_0 to P4_3 become I/O ports, in which case the accessible area for each CS is 256 bytes.

2. In separate bus mode, these pins serve as the address bus.

3.

_____ ________ ______

If the data bus is 8-bit width, make sure the PM02 bit is set to “0” (RD, BHE, WR).

4. When accessing the area that uses a multiplexed bus, these pins output an indeterminate value during

a write.