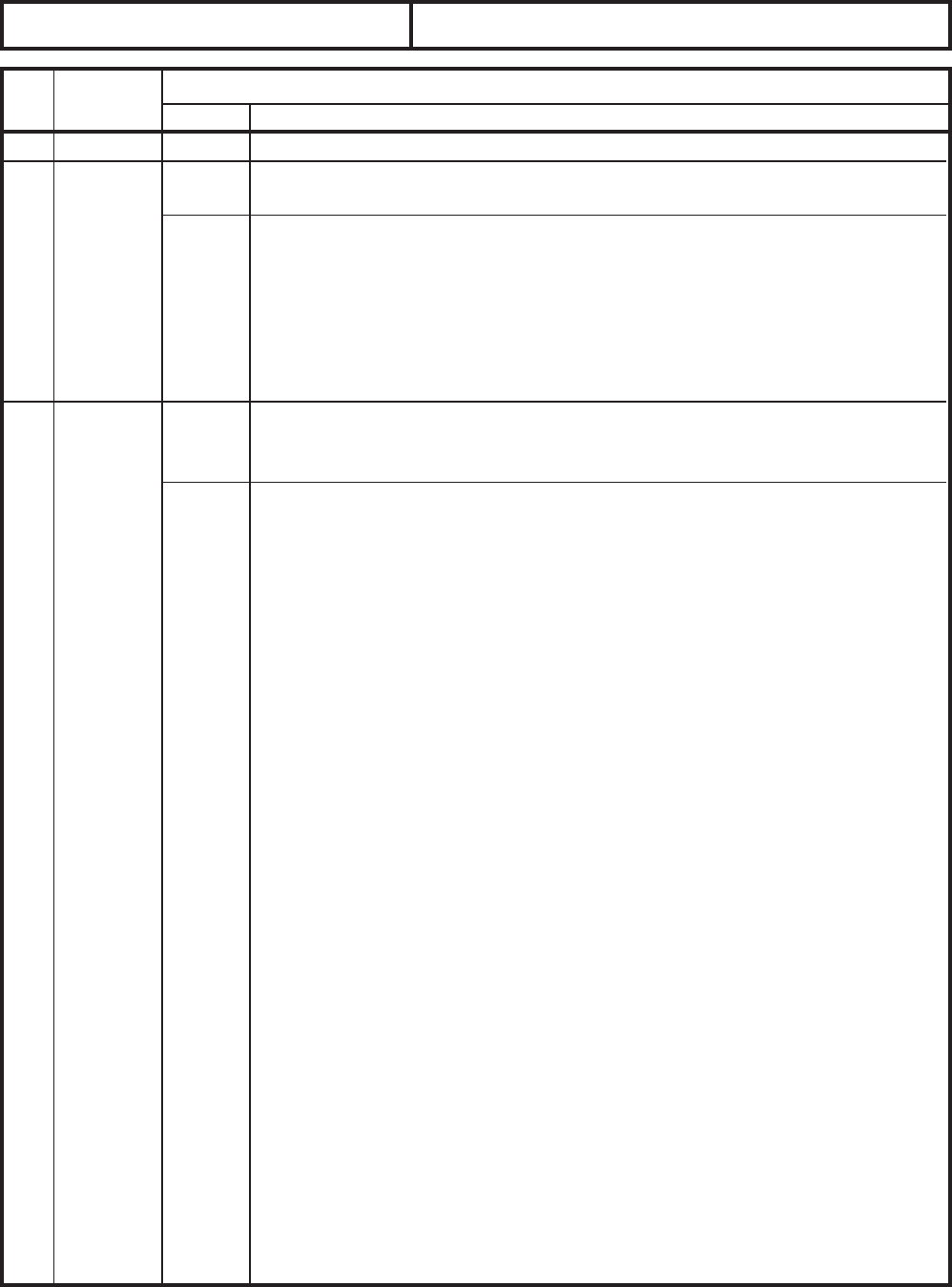

REVISION HISTORY

M16C/6N Group (M16C/6NK, M16C/6NM) Hardware Manual

Rev. Date

Description

Page Summary

C-1

1.00

Sep. 30, 2004

1.01

Nov. 01, 2004

1.10

Jul. 01, 2005

– First edition issued

– Revised edition issued

* Revised parts and revised contents are as follows (except for expressional change).

3 Table 1.2 Performance Outline of M16C/6N Group (128-pin Version: M16C/6NM)

• Interrupt: Internal interrupt source is revised from “32 sources” to “34 sources”.

270 Table 21.2 Recommended Operating Conditions (1)

• I

OH(peak): Unit is revised from “V” to “mA”.

271 Table 21.3 Recommended Operating Conditions (2)

• NOTE 3:

“VCC = 3.0 ± 0.3 V” is revised to “VCC = 3.3 ± 0.3 V”.

291 22.9.1.2 Timer A (Event Counter Mode) is revised.

– Revised edition issued

* The contents of product are revised. (T/V-ver. is added.)

* Revised parts and revised contents are as follows (except for expressional change).

2 Table 1.1 Performance outline of M16C/6N Group (100-pin Version: M16C/6NM)

• Performance outline of T/V-ver. is added.

3 Table 1.2 Performance outline of M16C/6N Group (128-pin Version: M16C/6NN)

• Performance outline of T/V-ver. is added.

5 Table 1.3 Product List is revised. (T/V-ver. is added.)

Figure 1.2 Type No., Memory Size, and Package: “Characteristics” is added.

13 FIgure 4.1 SFR Information (1): The value of After Reset in CM2 Register is revised.

19 Figure 4.7 SFR Information (7): NOTE 1 is revised.

39 Figure 7.4 CM2 Register: The value of After Reset is revised.

55 Figure 7.13 State Transition in Normal Operation Mode: NOTE 7 is revised.

78 9.10 Address Match Interrupt: After of 13th line

• “Note that when using the external bus in 8-bit width, no address match interrupts

can be used for external areas.” is deleted.

176 Figure 14.37 (upper) SiC Register: NOTE 4 is revised.

207 Figure 18.6 C0MCTLj and C1MCTLj Registers

• RemActive bit: Function is revised.

• RspLock bit: Bit Name is revised.

• NOTE 2 is revised.

208 Figure 18.7 C0CTLR and C1CTLR Registers (upper)

• LoopBack bit: The expression of Function is revised.

• BasicCAN bit: The expression of Function is revised.

Figure 18.7 C0CTLR and C1CTLR Registers (lower)

• TSPreScale bit: Bit Symbol is revised. (“Bit1, Bit0” is deleted.)

• TSReset bit: The expression of Function is revised.

• RetBusOff bit: The expression of Function is revised.

• RXOnly bit: The expression of Function is revised.

209 Figure 18.8 C0STR and C1STR Registers (upper): NOTE 1 is deleted.

Figure 18.8 C0STR and C1STR Registers (lower)

• State_LoopBack bit: The expression of Function is revised.

• State_BasicCAN bit: The expression of Function is revised.