Rev.2.00 Nov 28, 2005 page 50 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 7. Bus

Under development

This document is under development and its contents are subject to change.

__________

HOLD > DMAC > CPU

__________

7.2.7 HOLD Signal

This signal is used to transfer control of the bus from CPU or DMAC to an external circuit. When the input

__________

on HOLD pin is pulled low, the microcomputer is placed in a hold state after the bus access then in

__________

process finishes. The microcomputer remains in a hold state while the HOLD pin is held low, during which

__________

time the HLDA pin outputs a low-level signal.

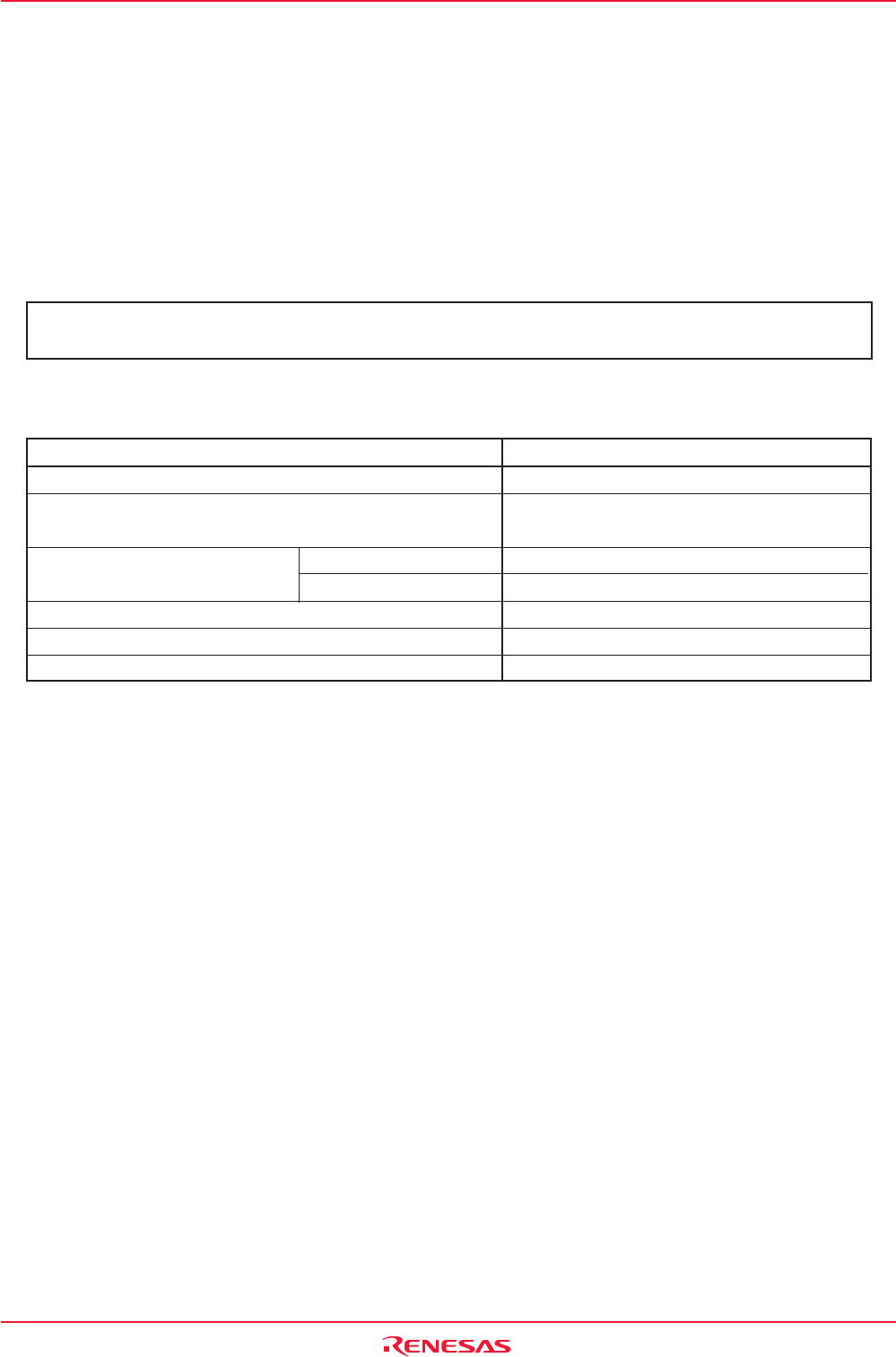

Table 7.5 shows the microcomputer status in the hold state.

__________

Bus-using priorities are given to HOLD, DMAC, and CPU in order of decreasing precedence (see Figure

7.5 Bus-using Priorities). However, if the CPU is accessing an odd address in word units, the DMAC

cannot gain control of the bus during two separate accesses.

Figure 7.5 Bus-using Priorities

Table 7.5 Microcomputer Status in Hold State

NOTES:

1. When I/O port function is selected.

2. The watchdog timer does not stop when the PM22 bit in the PM2 register is set to “1” (the count source

for the watchdog timer is the on-chip oscillator clock).

7.2.8 BCLK Output

If the PM07 bit in the PM0 register is set to “0” (output enable), a clock with the same frequency as that

of the CPU clock is output as BCLK from the BCLK pin. Refer to 8.2 CPU Clock and Peripheral Function

Clock.

Table 7.6 shows the pin functions for each processor mode.

Item Status

BCLK Output

_______ _______ ______ _________ _________

A0 to A19, D0 to D15, CS0 to CS3, RD, WRL, WRH, High-impedance

______ ________

WR, BHE

I/O Ports P0, P1, P3, P4

(1)

High-impedance

P6 to P10 Maintains status when hold signal is received

__________

HLDA Output “L”

Internal Peripheral Circuits ON (but watchdog timer stops

(2)

)

ALE Signal Undefined