Rev.2.00 Nov 28, 2005 page 334 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 22. Electric Characteristics (T/V-ver.)

Under development

This document is under development and its contents are subject to change.

Table 22.53 Flash Memory Version Electrical Characteristics

(1)

2

150

150

ms

µs

µs

Time for Internal Power Supply Stabilization During Powering-On

STOP Release Time

Low Power Dissipation Mode Wait Mode Release Time

td(P-R)

td(R-S)

td(W-S)

Symbol

Parameter

Min.

Standard

Unit

Measuring

Condition

Max.

Typ.

VCC = 4.2 to 5.5V

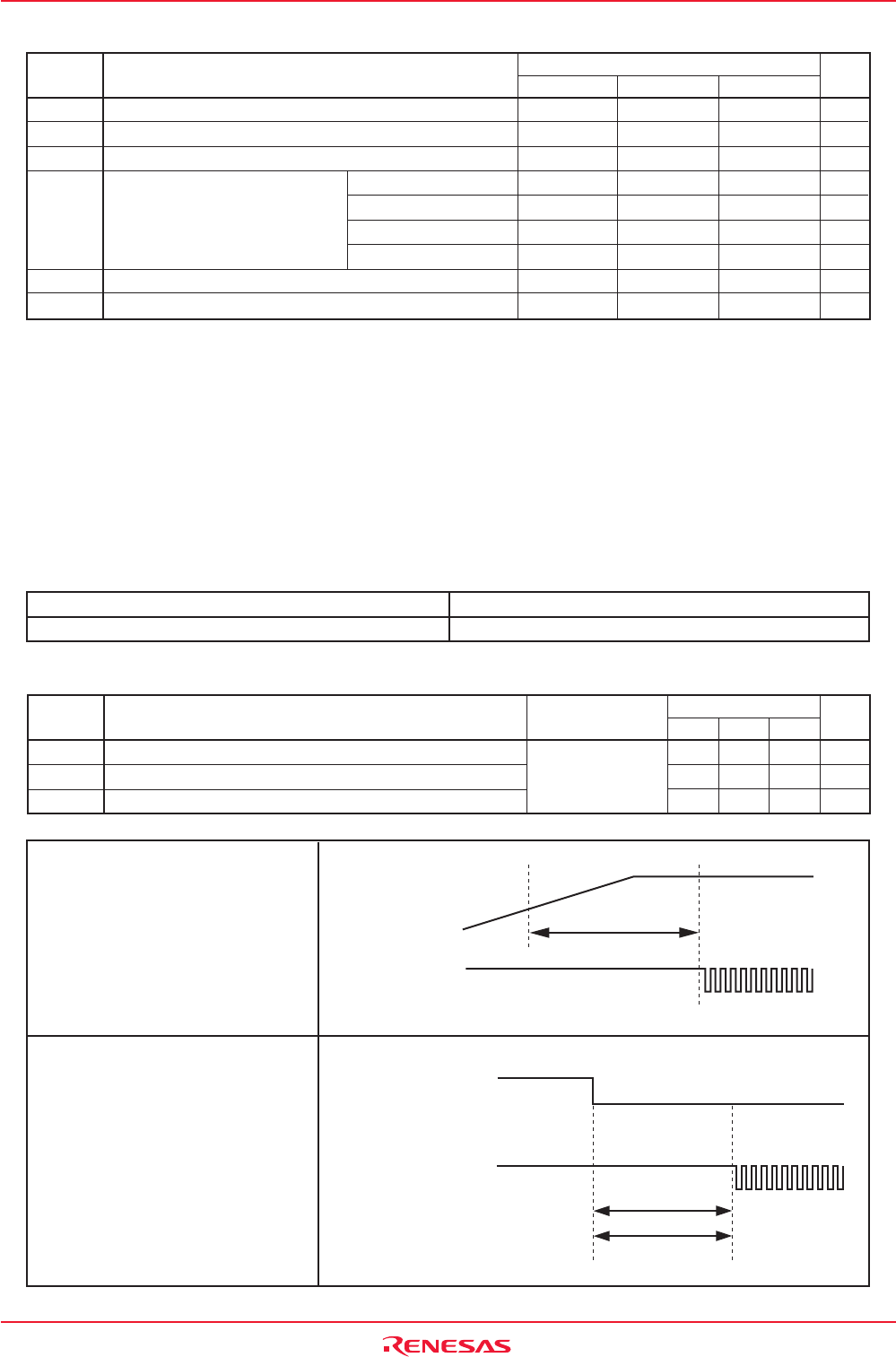

Table 22.55 Power Supply Circuit Timing Characteristics

CPU clock

VCC

t

d(P-R)

td(P-R)

Time for Internal Power Supply

Stabilization During Powering-On

t

d(R-S)

STOP Release Time

t

d(W-S)

Low Power Dissipation Mode

Wait Mode Release Time

CPU clock

td(W-S)

td(R-S)

(b)

(a)

Interrupt for

(a) Stop mode release

or

(b) Wait mode release

VCC = 5.0 ± 0.5V

Flash Read Operation VoltageFlash Program, Erase Voltage

VCC = 4.2 to 5.5V

NOTES:

1. Referenced to VCC = 4.5 to 5.5V, Topr = 0 to 60°C unless otherwise specified.

2. Program and Erase Endurance refers to the number of times a block erase can be performed.

If the program and erase endurance is n (n = 100), each block can be erased n times.

For example, if a 4-Kbyte block A is erased after writing 1 word data 2,048 times, each to a different address,

this counts as one program and erase endurance. Data cannot be written to the same address more than

once without erasing the block. (Rewrite prohibited)

3. n denotes the number of blocks to erase.

Table 22.54 Flash Memory Version Program/Erase Voltage and Read Operation Voltage Characteristics

(at Topr = 0 to 60°C)

200

200

4

4

4

4

4 ✕ n

(3)

15

cycle

µs

µs

s

s

s

s

s

µs

Program and Erase Endurance

(2)

Word Program Time (VCC = 5.0V)

Lock Bit Program Time

Block Erase Time 4-Kbyte block

(VCC = 5.0V) 8-Kbyte block

32-Kbyte block

64-Kbyte block

Erase All Unlocked Blocks Time

Flash Memory Circuit Stabilization Wait Time

Parameter

Min.

Standard

Unit

Max.Typ.

25

25

0.3

0.3

0.5

0.8

Symbol

-

-

-

-

-

tps

100

Figure 22.22 Power Supply Circuit Timing Diagram