Rev.2.00 Nov 28, 2005 page 53 of 378

REJ09B0124-0200

M16C/6N Group (M16C/6NK, M16C/6NM) 7. Bus

Under development

This document is under development and its contents are subject to change.

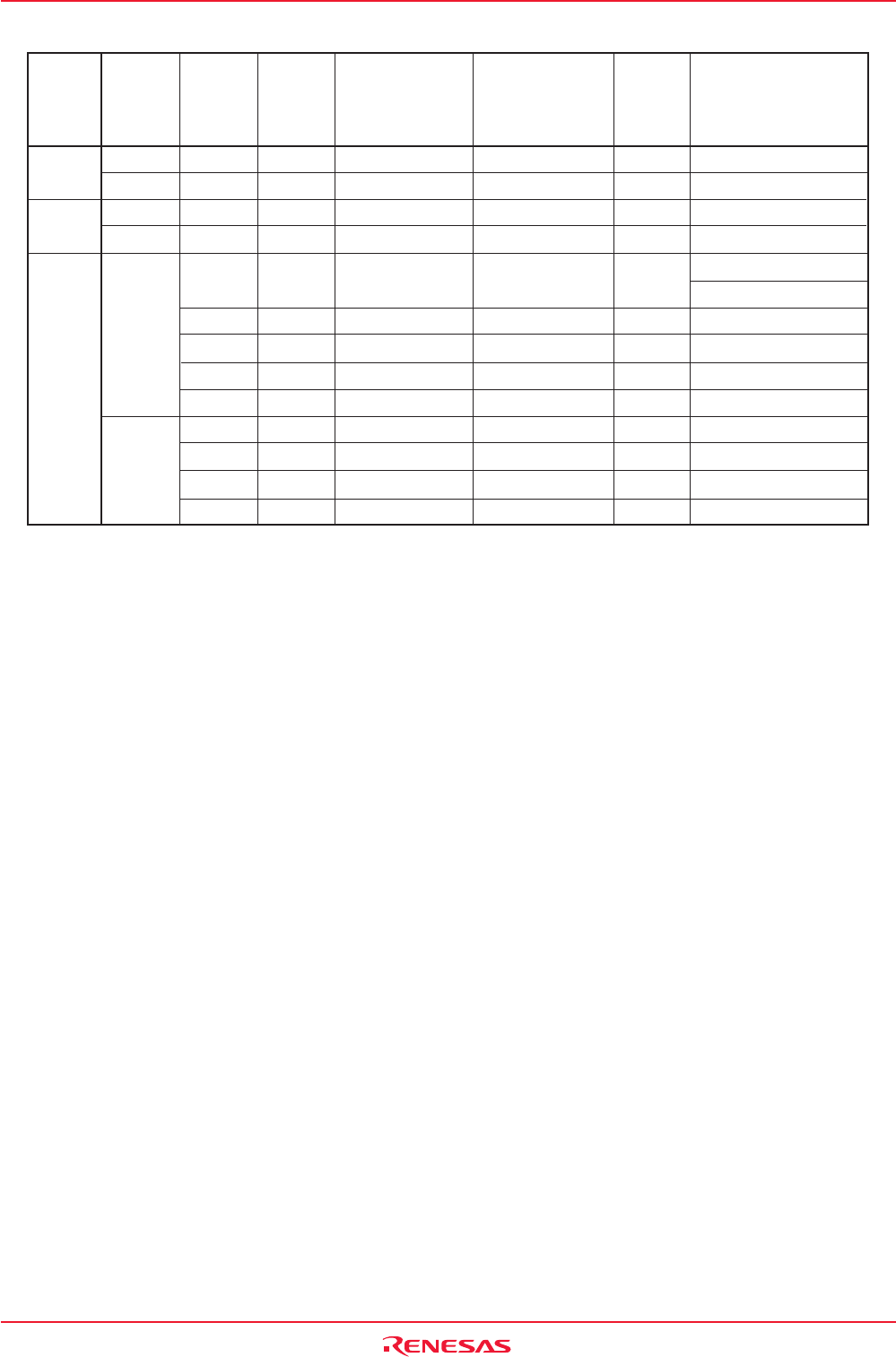

Table 7.8 Software Wait Related Bits and Bus Cycles

Area

Bus Mode

SFR

Internal

ROM, RAM

External

Area

-

-

-

-

Separate

Bus

Multiplexed

Bus

(2)

PM1 Register

PM17 Bit

(5)

-

-

0

1

0

-

-

-

1

-

-

-

1

3 BCLK cycles

(4)

2 BCLK cycles

(4)

1 BCLK cycle

(3)

2 BCLK cycles

1 BCLK cycle (read)

2 BCLK cycles (write)

2 BCLK cycles

(3)

3 BCLK cycles

4 BCLK cycles

2 BCLK cycles

3 BCLK cycles

3 BCLK cycles

4 BCLK cycles

3 BCLK cycles

Bus Cycle

-

-

-

-

1

0

0

0

0

0

0

0

0

-

-

-

-

00b

00b

01b

10b

00b

00b

01b

10b

00b

CSR Register

CS3W Bit

(1)

CS2W Bit

(1)

CS1W Bit

(1)

CS0W Bit

(1)

CSE Register

CS31W to CS30W Bits

CS21W to CS20W Bits

CS11W to CS10W Bits

CS01W to CS00W Bits

NOTES:

1.

________

To use the RDY signal, set this bit to “0 ”.

2. To access in multiplexed bus mode, set the corresponding bit of CS0W to CS3W to “0” (with wait state).

3. After reset, the PM17 bit is set to “0” (without wait state), all of the CS0W to CS3W bits are set to “0”

_______ _______

(with wait state), and the CSE register is set to “00h” (one wait state for CS0 to CS3). Therefore, the

internal RAM and internal ROM are accessed with no wait state, and all external areas are accessed

with one wait state.

4. When the selected CPU clock source is the PLL clock, the number of wait cycles can be altered by the

PM20 bit in the PM2 register. When using PLL clock over 16 MHz, be sure to set the PM20 bit to “0”

(2 wait cycles).

5. When the PM17 bit is set to “1” and access an external area, set the CSiW bits (i = 0 to 3) to “0” (with

wait sate).

Software

Wait

-

-

No wait

1 wait

No wait

1 wait

2 waits

3 waits

1 wait

1 wait

2 waits

3 waits

1 wait

0

1

-

-

-

-

-

-

-

-

-

-

-

PM2 Register

PM20 Bit