SAM88RI INSTRUCTION SET S3C9228/P9228

6-18

CP — Compare

CP dst,src

Operation: dst – src

The source operand is compared to (subtracted from) the destination operand, and the

appropriate flags are set accordingly. The contents of both operands are unaffected by the

comparison.

Flags: C: Set if a "borrow" occurred (src > dst); cleared otherwise.

Z: Set if the result is "0"; cleared otherwise.

S: Set if the result is negative; cleared otherwise.

V: Set if arithmetic overflow occurred, that is, if the operands were of opposite signs and the

sign of the result is of the same as the sign of the source operand; cleared otherwise.

D: Unaffected.

H: Unaffected.

Format:

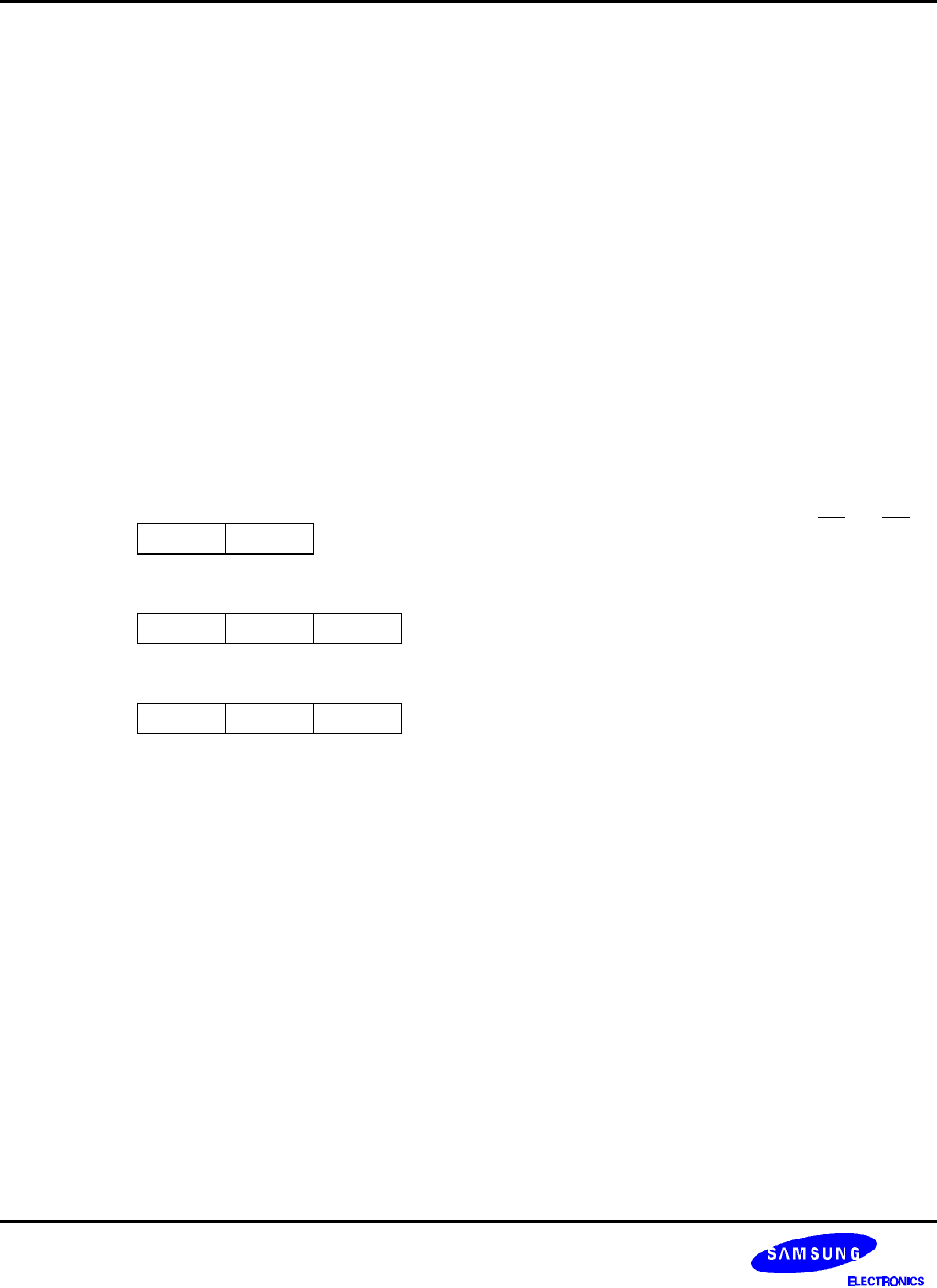

Bytes Cycles Opcode

(Hex)

Addr Mode

dst src

opc dst | src 2 4 A2 r r

6 A3 r lr

opc src dst 3 6 A4 R R

6 A5 R IR

opc dst src 3 6 A6 R IM

Examples: 1. Given: R1 = 02H and R2 = 03H:

CP R1,R2 → Set the C and S flags

Destination working register R1 contains the value 02H and source register R2 contains the value

03H. The statement "CP R1,R2" subtracts the R2 value (source/subtrahend) from the R1 value

(destination/minuend). Because a "borrow" occurs and the difference is negative, C and S are "1".

2. Given: R1 = 05H and R2 = 0AH:

CP R1,R2

JP UGE,SKIP

INC R1

SKIP LD R3,R1

In this example, destination working register R1 contains the value 05H which is less than the

contents of the source working register R2 (0AH). The statement "CP R1,R2" generates C = "1"

and the JP instruction does not jump to the SKIP location. After the statement "LD R3,R1"

executes, the value 06H remains in working register R3.