CLOCK CIRCUITS S3C9228/P9228

7-4

SYSTEM CLOCK CONTROL REGISTER (CLKCON)

The system clock control register, CLKCON, is located in address D4H. It is read/write addressable and has the

following functions:

— Oscillator IRQ wake-up function enable/disable

— Oscillator frequency divide-by value

CLKCON register settings control whether or not an external interrupt can be used to trigger a Stop mode release

(This is called the “IRQ wake-up” function). The IRQ “wake-up” enable bit is CLKCON.7.

After a reset, the external interrupt oscillator wake-up function is enabled, the main oscillator is activated, and the

fx/16 (the slowest clock speed) is selected as the CPU clock. If necessary, you can then increase the CPU clock

speed to fx, fx/2, or fx/8 by setting the CLKCON, and you can change system clock from main clock to sub clock

by setting the OSCCON.

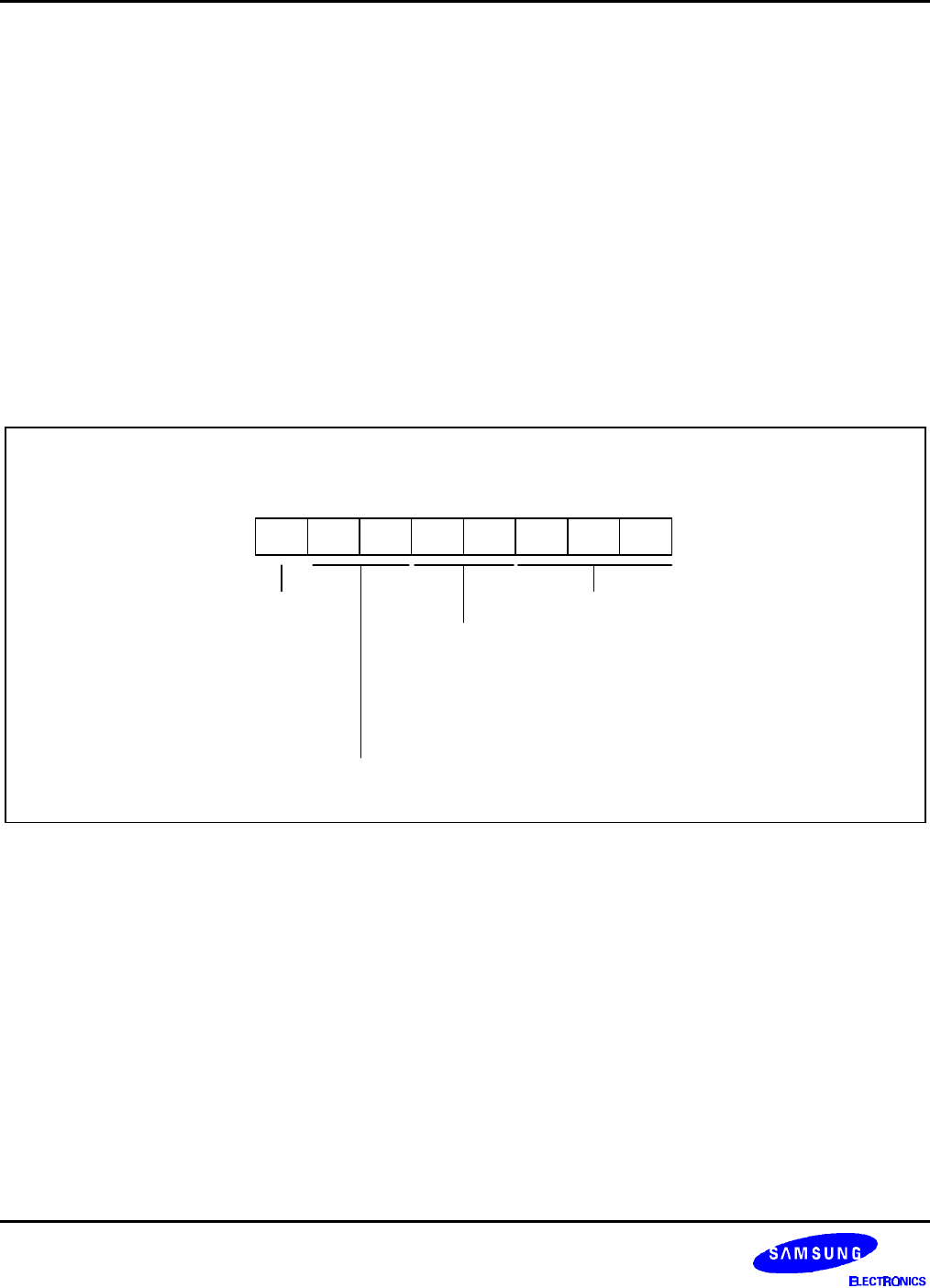

System Clock Control Register (CLKCON)

D4H, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

Not used for S3C9228 (must keep always "0")

Divide-by selection bits for

CPU clock frequency:

00 = fxx/16

01 = fxx/8

10 = fXx/2

11 = fxx

Oscillator IRQ wake-up enable bit:

0 = Enable IRQ for main oscillator

wake-up function in power down

mode

1 = Disable IRQ for main oscillator

wake-up function in power down

mode

Not used for S3C92228 (must keep always "0")

Figure 7-7. System Clock Control Register (CLKCON)