S3C9228/P9228 SAM88RCRI INSTRUCTION SET

6-41

RR — Rotate Right

RR dst

Operation: C ¨ dst (0)

dst (7) ¨ dst (0)

dst (n) ¨ dst (n + 1), n = 0–6

The contents of the destination operand are rotated right one bit position. The initial value of bit

zero (LSB) is moved to bit 7 (MSB) and also replaces the carry flag (C).

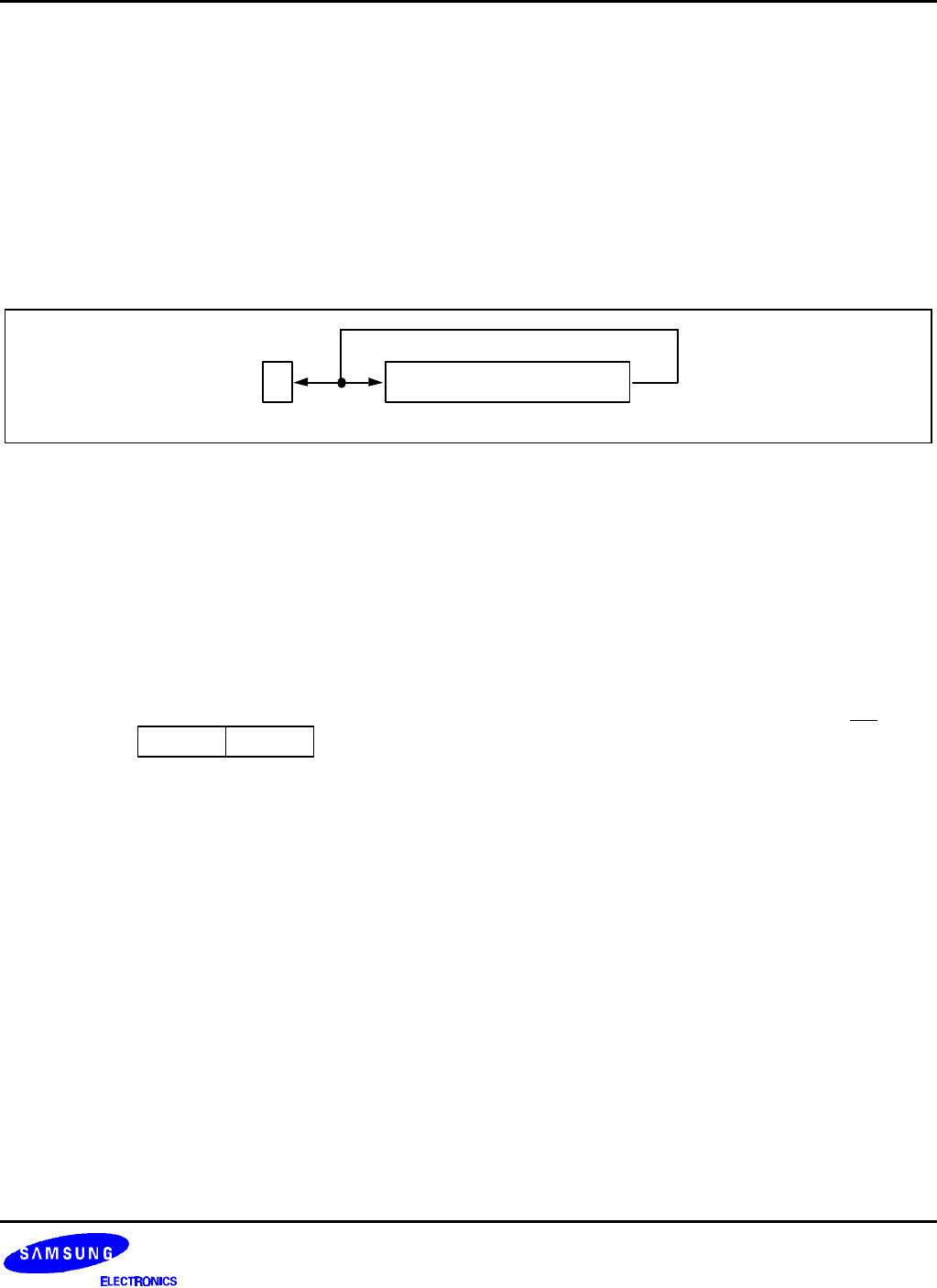

C

7 0

Flags: C: Set if the bit rotated from the least significant bit position (bit zero) was "1".

Z: Set if the result is "0"; cleared otherwise.

S: Set if the result bit 7 is set; cleared otherwise.

V: Set if arithmetic overflow occurred, that is, if the sign of the destination changed during

rotation; cleared otherwise.

D: Unaffected.

H: Unaffected.

Format:

Bytes Cycles Opcode

(Hex)

Addr Mode

dst

opc dst 2 4 E0 R

4 E1 IR

Examples: Given: Register 00H = 31H, register 01H = 02H, and register 02H = 17H:

RR 00H → Register 00H = 98H, C = "1"

RR @01H → Register 01H = 02H, register 02H = 8BH, C = "1"

In the first example, if general register 00H contains the value 31H (00110001B), the statement

"RR 00H" rotates this value one bit position to the right. The initial value of bit zero is moved to

bit 7, leaving the new value 98H (10011000B) in the destination register. The initial bit zero also

resets the C flag to "1" and the sign flag and overflow flag are also set to "1".