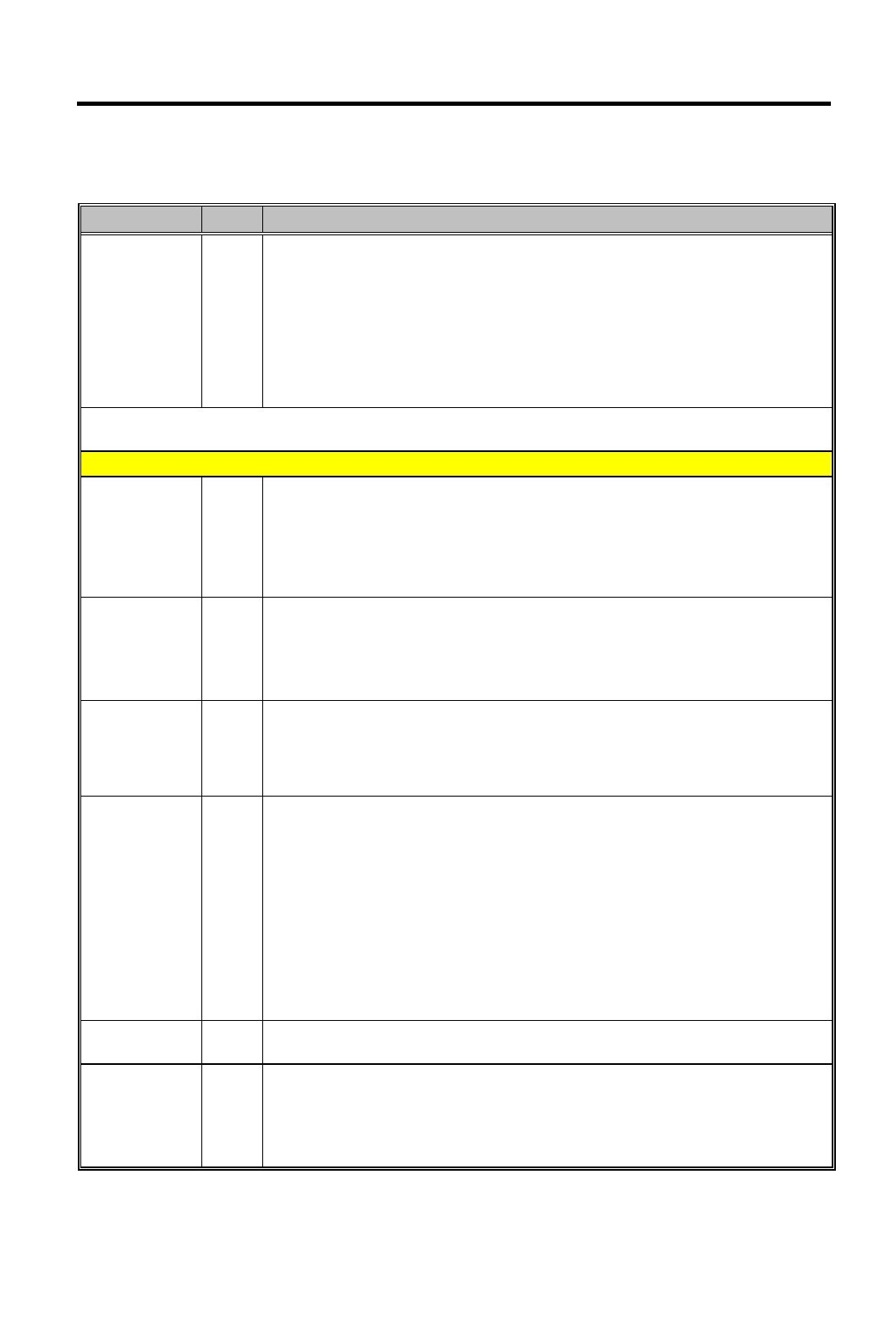

Major Chips Description 2-11

Table 2-2 82371AB Pin Descriptions

Name Type Description

TRDY# I/O

TARGET READY. TRDY# indicates PIIX4’s ability to complete the current data

phase of the transaction. TRDY# is used in conjunction with IRDY#. A data phase

is completed when both TRDY# and IRDY# are sampled asserted. During a read,

TRDY# indicates that PIIX4, as a Target, has place valid data on AD[31:0].

During a write, it indicates PIIX4, as a Target is prepared to latch data. TRDY# is

an input to PIIX4 when PIIX4 is the Initiator and an output when PIIX4 is a Target.

TRDY# is tri-stated from the leading edge of PCIRST#. TRDY# remains tri-stated

until driven by PIIX4 as a slave.

During Reset: High-Z After Reset: High-Z During POS: High-Z

Note: All of the signals in the host interface are described in the Pentium Processor data sheet. The

preceding table highlights PIIX4 specific uses of these signals.

ISA BUS INTERFACE

AEN O

ADDRESS ENABLE. AEN is asserted during DMA cycles to prevent I/O slaves

from misinterpreting DMA cycles as valid I/O cycles. When negated, AEN

indicates that an I/O slave may respond to address and I/O commands. When

asserted, AEN informs I/O resources on the ISA bus that a DMA transfer is

occurring. This signal is also driven high during PIIX4 initiated refresh cycles.

During Reset: High-Z After Reset: Low During POS: Low

BALE O

BUS ADDRESS LATCH ENABLE. BALE is asserted by PIIX4 to indicate that the

address (SA[19:0], LA[23:17]) and SBHE# signal lines are valid. The LA[23:17]

address lines are latched on the trailing edge of BALE. BALE remains asserted

throughout DMA and ISA master cycles.

During Reset: High-Z After Reset: Low During POS: Low

IOCHK#/

GPI0

I

I/O CHANNEL CHECK. IOCHK# can be driven by any resource on the ISA bus.

When asserted, it indicates that a parity or an uncorrectable error has occurred

for a device or memory on the ISA bus. A NMI will be generated to the CPU if the

NMI generation is enabled. If the EIO bus is used, this signal becomes a general

purpose input.

IOCHRDY I/O

I/O CHANNEL READY. Resources on the ISA Bus negate IOCHRDY to indicate

that wait states are required to complete the cycle. This signal is normally high.

IOCHRDY is an input when PIIX4 owns the ISA Bus and the CPU or a PCI agent

is accessing an ISA slave, or during DMA transfers. IOCHRDY is output when an

external ISA Bus Master owns the ISA Bus and is accessing DRAM or a PIIX4

register. As a PIIX4 output, IOCHRDY is driven inactive (low) from the falling

edge of the ISA commands. After data is available for an ISA master read or

PIIX4 latches the data for a write cycle, IOCHRDY is asserted for 70 ns. After 70

ns, PIIX4 floats IOCHRDY. The 70 ns includes both the drive time and the time it

takes PIIX4 to float IOCHRDY. PIIX4 does not drive this signal when an ISA Bus

master is accessing an ISA Bus slave.

During Reset: High-Z After Reset: High-Z During POS: High-Z

IOCS16# I

16-BIT I/O CHIP SELECT. This signal is driven by I/O devices on the ISA Bus to

indicate support for 16-bit I/O bus cycles.

IOR# I/O

I/O READ. IOR# is the command to an ISA I/O slave device that the slave may

drive data on to the ISA data bus (SD[15:0]). The I/O slave device must hold the

data valid until after IOR# is negated. IOR# is an output when PIIX4 owns the ISA

Bus. IOR# is an input when an external ISA master owns the ISA Bus.

During Reset: High-Z After Reset: High During POS: High