MultiProcessor Specification

3-8 Version 1.4

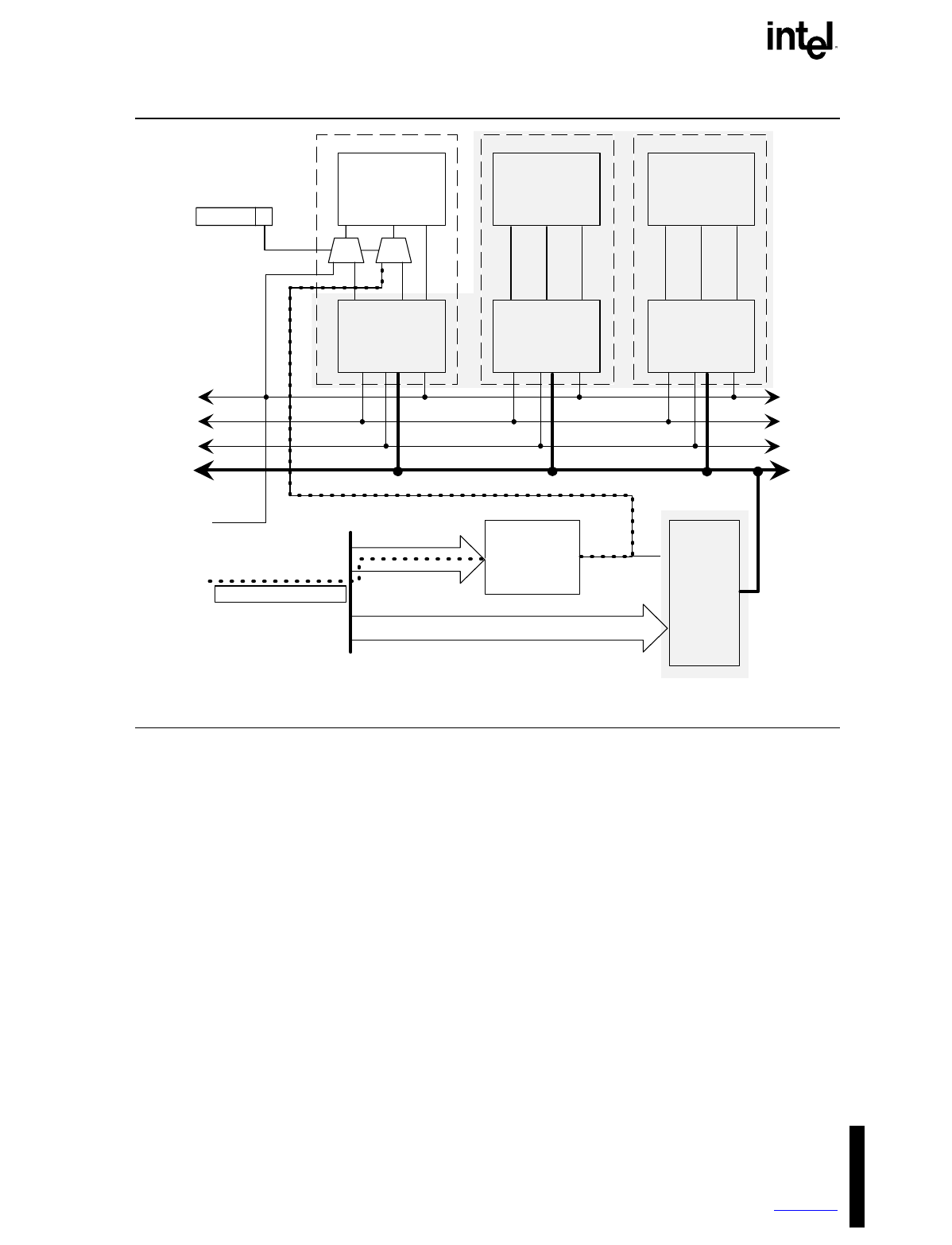

LINTIN0 LINTIN1

NMI

NMI

INTR

CPU 1

LINTIN0 LINTIN1 LINTIN0 LINTIN1

NMI INTR

CPU 2

NMI INTR

CPU 3

REG.

MARK

BSP AP1 AP2

LOCAL

APIC

1

LOCAL

APIC

2

LOCAL

APIC

3

RESET

LINTIN0

LINTIN1

ICC BUS

IMCR

E0

INTR

I/O

APIC

8259A-

EQUIVALENT

PICS

INTERRUPT INPUTS

SHADED AREAS INDICATE UNUSED CIRCUITS. DOTTED LINE SHOWS INTERRUPT PATH.

Figure 3-2. PIC Mode

The IMCR is supported by two read/writable or write-only I/O ports, 22h and 23h, which receive

address and data respectively. To access the IMCR, write a value of 70h to I/O port 22h, which

selects the IMCR. Then write the data to I/O port 23h. The power-on default value is zero, which

connects the NMI and 8259 INTR lines directly to the BSP. Writing a value of 01h forces the

NMI and 8259 INTR signals to pass through the APIC.

The IMCR must be cleared after a system-wide INIT or RESET to enable the PIC Mode as default.

(Refer to Section 3.7 for information on the INIT and RESET signals.)

The IMCR is optional if PIC Mode is not implemented. The IMCRP bit of the MP feature

information bytes (refer to Chapter 4) enables the operating system to detect whether the IMCR is

implemented.