MultiProcessor Specification

4-12 Version 1.4

4.3.3 I/O APIC Entries

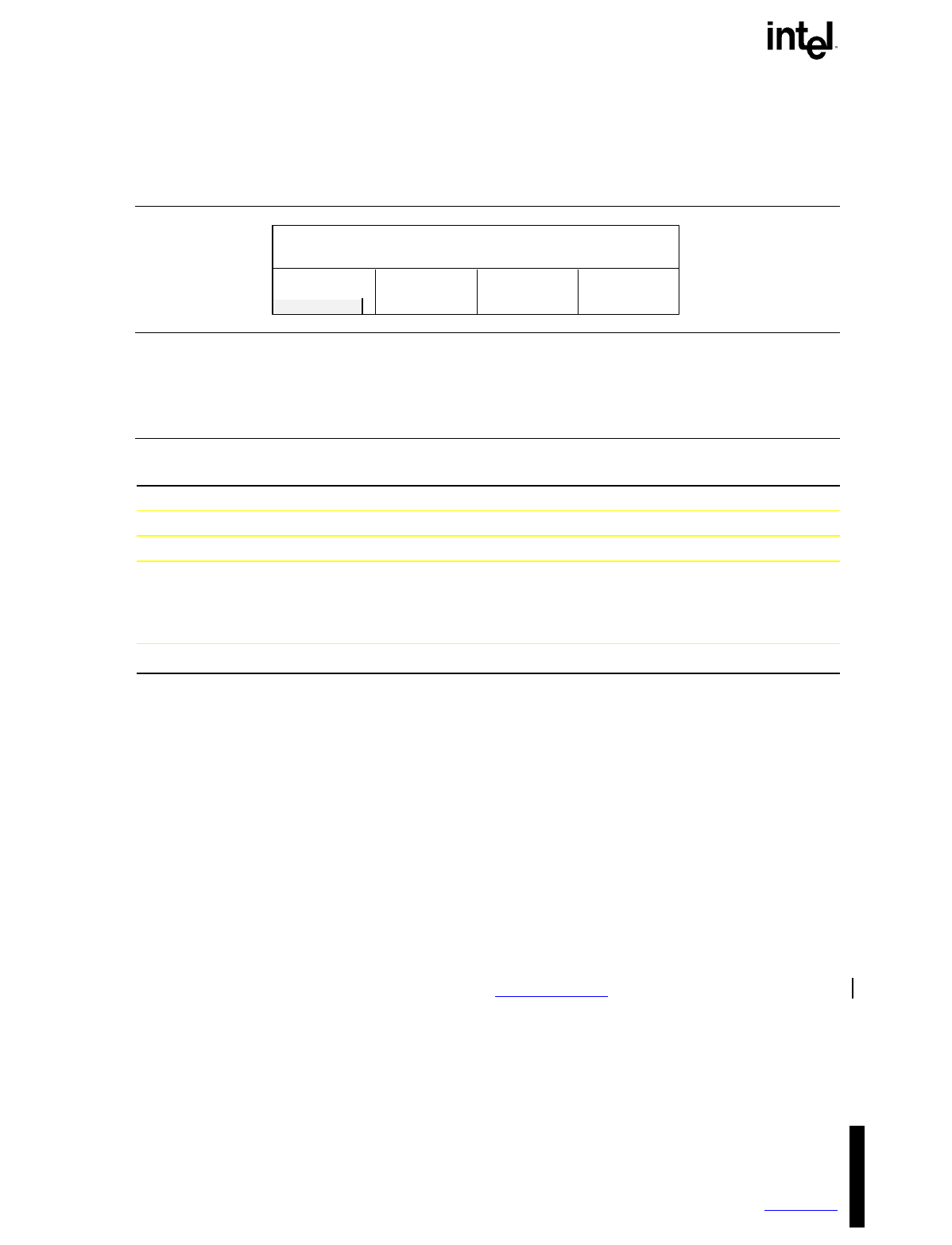

The configuration table contains one or more entries for I/O APICs. Figure 4-6 shows the format

of each I/O APIC entry, and Table 4-9 explains each field.

00H

04H

31 07815162324

31 07815162324

ENTRY TYPE

2

I/O APIC ID

I/O APIC

VERSION #

MEMORY-MAPPED ADDRESS OF I/O APIC

I/O APIC FLAGS

E

N

RESERVED

Figure 4-6. I/O APIC Entry

Table 4-9. I/O APIC Entry Fields

Field

Offset

(in bytes:bits)

Length

(in bits) Description

ENTRY TYPE 0 8 A value of 2 identifies an I/O APIC entry.

I/O APIC ID 1 8 The ID of this I/O APIC.

I/O APIC VERSION # 2 8 Bits 0–7 of the I/O APIC’s version register.

I/O APIC FLAGS: EN 3:0 1 If zero, this I/O APIC is unusable, and the

operating system should not attempt to access

this I/O APIC.

At least one I/O APIC must be enabled.

I/O APIC ADDRESS 4 32 Base address for this I/O APIC.

4.3.4 I/O Interrupt Assignment Entries

These entries indicate which interrupt source is connected to each I/O APIC interrupt input. There

is one entry for each I/O APIC interrupt input that is connected. Figure 4-7 shows the format of

each entry, and Table 4-10 explains each field. Appendix D provides the semantics for encoding

PCI interrupts.

The MP specification enables significantly more interrupt sources than the standard AT

architecture by using I/O APICs. When using I/O APICs, it is preferable that the buses do not

share interrupts with the other buses. Bus implementations that share interrupts, such as the PCI

and VL local buses, support their bus interrupts by overloading them into another bus space. These

buses can be supported in one of the following two ways:

1. Interrupt Assignment Entries for each of the bus interrupts are listed in the MP configuration

table. Each interrupt destination matches the destination of another interrupt source interrupt

that this interrupt shares. For example, if PCI-Device1/INTA#

has the same vector as

ISA-IRQ2, then both Interrupt Assignment Entries for these vectors would refer to the same

destination I/O APIC and INTIN#.