Version 1.4 C-1

C

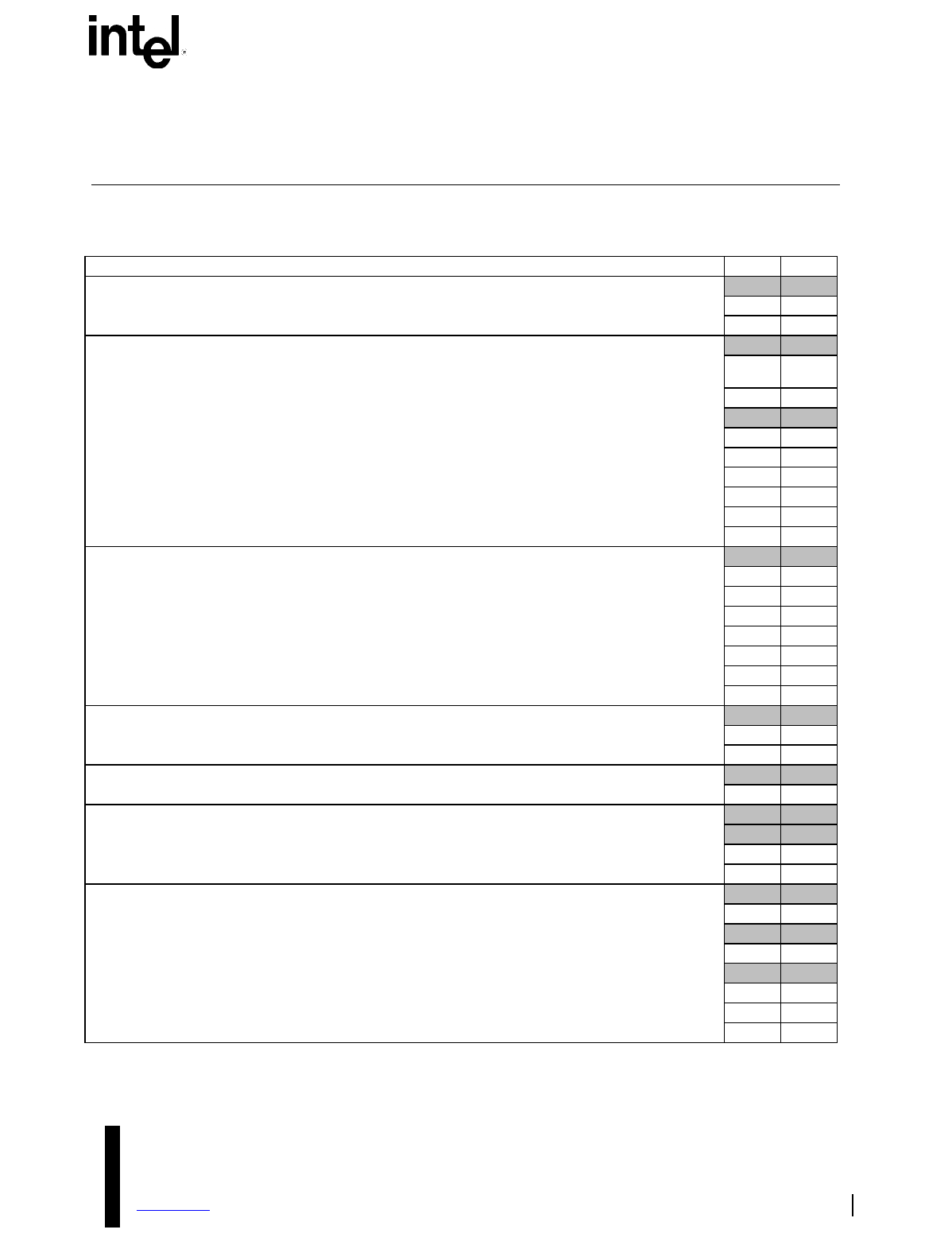

System Compliance Checklist

Any "NO" answer indicates non-compliance.

Condition YES NO

1. PC/AT Compatibility

Does system contain all necessary MP-compatible circuitry?

Will system boot and run DOS and Microsoft Windows?

2. Memory Subsystem

Are system memory address map, cacheability, and shareability consistent with

definitions in Table 3-1?

Are memory-mapped I/O devices located at the top of the memory address space?

If the system has external cache:

Is cache coherence maintained by hardware?

Is cache flushing supported by hardware?

Is cache flushing limited to the local caches?

Are all locked operations visible to all processors?

Are locked operations guaranteed on aligned memory operations?

Are memory writes observed externally in same order as programmed?

3. Multiprocessor Interrupt Control

Does each processor have its own local APIC?

Is there a processor designated for booting?

Does system support either PIC Mode or Virtual Wire Mode at power-on?

Is Symmetric I/O Mode implemented?

Are all APIC IDs unique?

Are all local APIC IDs assigned by hardware or BIOS?

Do local APIC IDs begin with zero?

4. Reset Support

Does system implement software-initiated processor-specific INIT (INIT IPI)?

Do system soft and hard resets reset all processors?

5. APIC Interval Timer

On 82489DX, is CLK the only clock source of the APIC timer?

6. Fault Resilient Booting

If fault resilient booting feature is implemented:

Is fault resilient booting feature software transparent?

Are system signals: NMI, INTR, FERR#, IGNNE#, and A20M connected to BSP?

7. MP Floating Pointer Structure and MP Configuration Table

Is the MP floating pointer structure implemented?

If the MP feature byte 1 (default configuration type) is nonzero:

Does the system correctly implement one of the default configurations?

If the MP feature byte 1 (default configuration type) is zero:

Has the system created a correct MP configuration table?

If the IMCR presence bit is set, is PIC Mode implemented?

If the IMCR presence bit is not set, is Virtual-Wire Mode implemented?