MP Configuration Table

Version 1.4 4-7

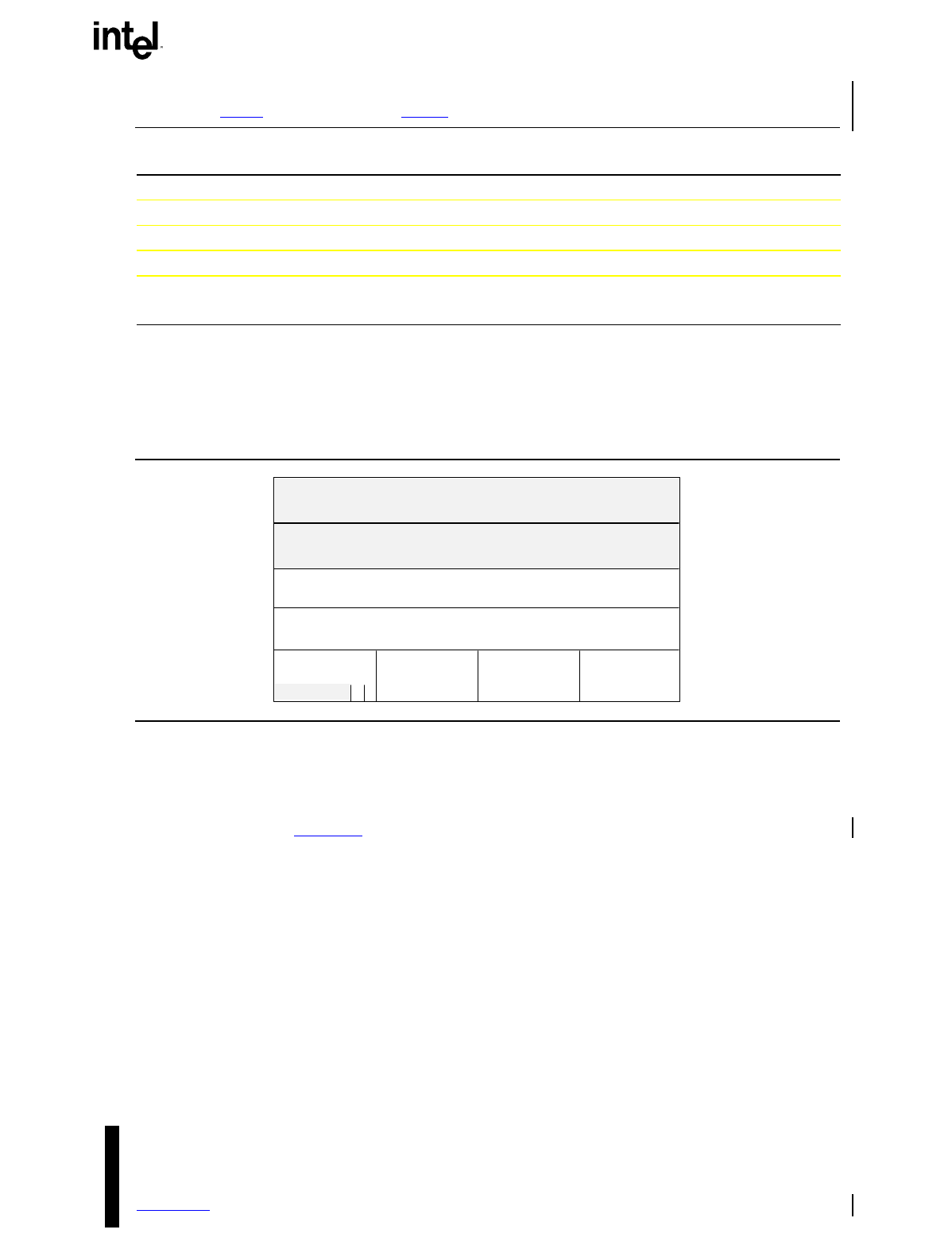

Table 4-3. Base MP Configuration Table Entry Types

Entry Description Entry Type Code*

Length

(in bytes) Comments

Processor 0 20 One entry per processor.

Bus 1 8 One entry per bus.

I/O APIC 2 8 One entry per I/O APIC.

I/O Interrupt Assignment 3 8 One entry per bus interrupt source.

Local Interrupt Assignment 4 8 One entry per system interrupt

source.

* All other type codes are reserved.

4.3.1 Processor Entries

Figure 4-4 shows the format of each processor entry, and Table 4-4 defines the fields.

RESERVED

RESERVED

31 0374811121516192023242728

CPU SIGNATURE

LOCAL APIC ID

CPU FLAGS

FEATURE FLAGS

31 0374811121516192023242728

00H

04H

08H

0CH

10H

LOCAL APIC

VERSION #

ENTRY TYPE

0

E

N

RESERVED

B

P

Figure 4-4. Processor Entry

In systems that use the MP configuration table, the only restriction placed on the assignment of

APIC IDs is that they be unique

. They do not need to be consecutive. For example, it is possible

for only APIC IDs 0, 2, and 4 to be present.