MP Configuration Table

Version 1.4 4-17

4.4 Extended MP Configuration Table Entries

A variable number of variable-length entries are located in memory, immediately following entries

in the base section of the MP configuration table described in Section 4.3. These entries compose

the extended section of the MP configuration table. Each entry in the extended section of the table

has three elements:

• ENTRY TYPE

• ENTRY LENGTH

• DATA

ENTRY TYPE and ENTRY LENGTH make up a header that is present in all extended

configuration table entries. The ENTRY TYPE and ENTRY LENGTH fields are eight bit

unsigned values. ENTRY LENGTH specifies the total length of the given configuration entry. The

length of the DATA field is two bytes less than the value specified by ENTRY LENGTH.

This scheme ensures that operating systems can parse all the entries in the extended MP

configuration table area, even if an entry type is unrecognized. Operating systems that find an

unknown entry type when parsing this section of the table should ignore the content and move on

to the next entry, until the offset from the end of the base table reaches the length that is specified

in the EXTENDED TABLE LENGTH field of the configuration table header. The ability to skip

entries with unrecognized type codes beyond those listed in Table 4-13 is essential since it is

anticipated that more types of entries will be added to this list over time.

The total length of the Extended MP configuration table depends upon the configuration of the

system. The entries are sorted on ENTRY TYPE in ascending order. Table 4-13 gives the meaning

of each value of ENTRY TYPE.

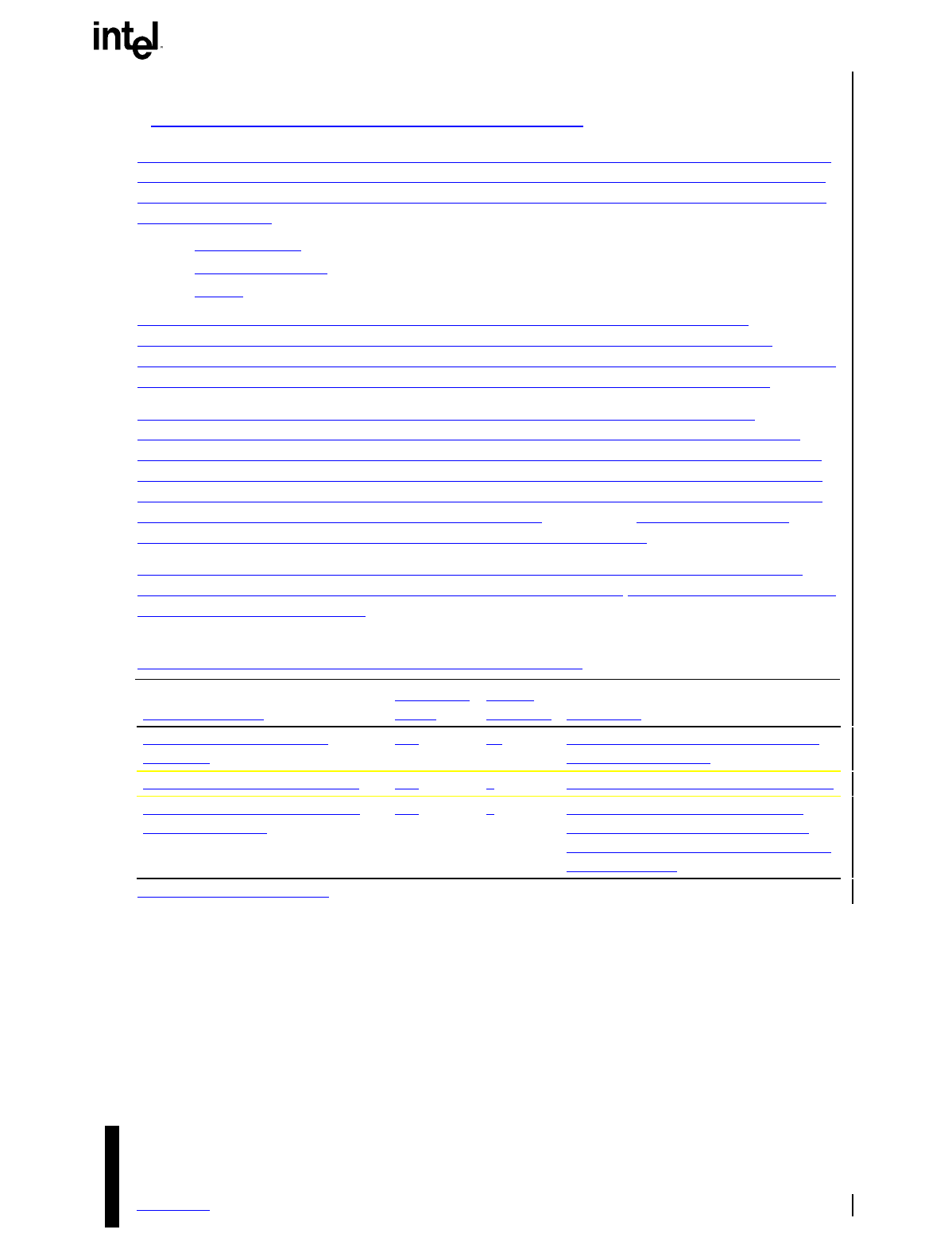

Table 4-13. Extended MP Configuration Table Entry Types

Entry Description

Entry Type

Code*

Length

(in bytes) Comments

SYSTEM ADDRESS SPACE

MAPPING

128 20 Entry to declare system visible memory

or I/O space on a bus.

BUS HIERARCHY DESCRIPTOR 129 8 Entry to describe I/O bus interconnection.

COMPATIBILITY BUS ADDRESS

SPACE MODIFIER

130 8 Entry to describe predefined address

ranges that modify the memory or I/O

space visible on a bus in order to support

ISA compatibility.

*

All other type codes are reserved.