MultiProcessor Specification

3-10 Version 1.4

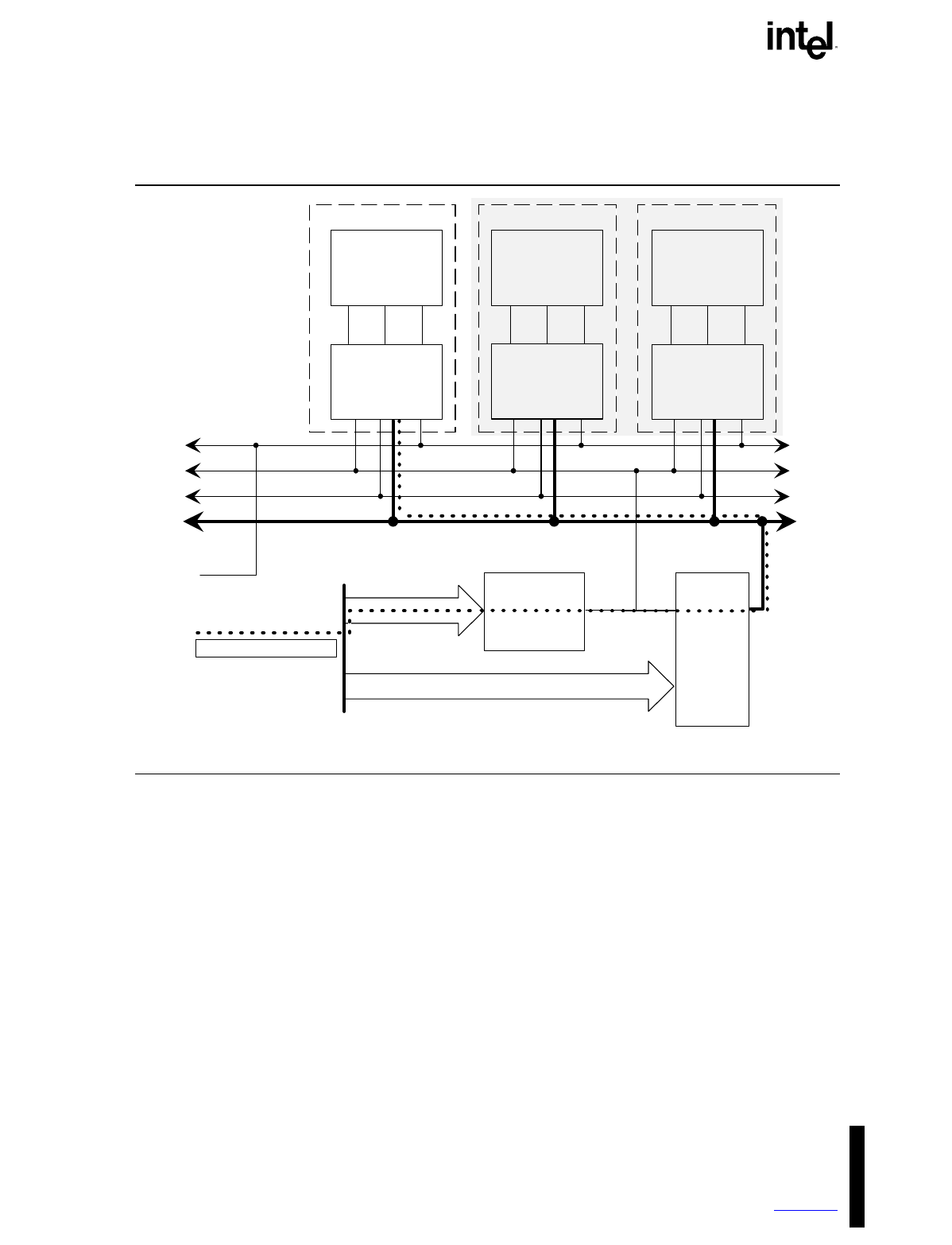

Figure 3-3 shows how Virtual Wire Mode can be implemented through the BSP’s local APIC. It is

also permissible to program the I/O APIC for Virtual Wire Mode, as shown in Figure 3-4. In this

case the interrupt signal passes through both the I/O APIC and the BSP’s local APIC.

LINTIN0 LINTIN1

NMI

NMI

INTR

CPU 1

LINTIN0 LINTIN1 LINTIN0 LINTIN1

NMI INTR

CPU 2

NMI INTR

CPU 3

REG.

MARK

BSP AP1 AP2

LOCAL

APIC

1

LOCAL

APIC

2

LOCAL

APIC

3

RESET

LINTIN0

LINTIN1

ICC BUS

INTR

I/O

APIC

8259A-

EQUIVALENT

PICS

INTERRUPT INPUTS

SHADED AREAS INDICATE UNUSED CIRCUITS. DOTTED LINE SHOWS INTERRUPT PATH.

Figure 3-4. Virtual Wire Mode via I/O APIC