Power Distribution Board Intel® Server Platform SR6850HW4 TPS

Revision 1.0

Intel order number D23151-001

66

+3.3V_AUX +3.3V_AUX

LATCH DIP PLUG

Adobe Sy stems

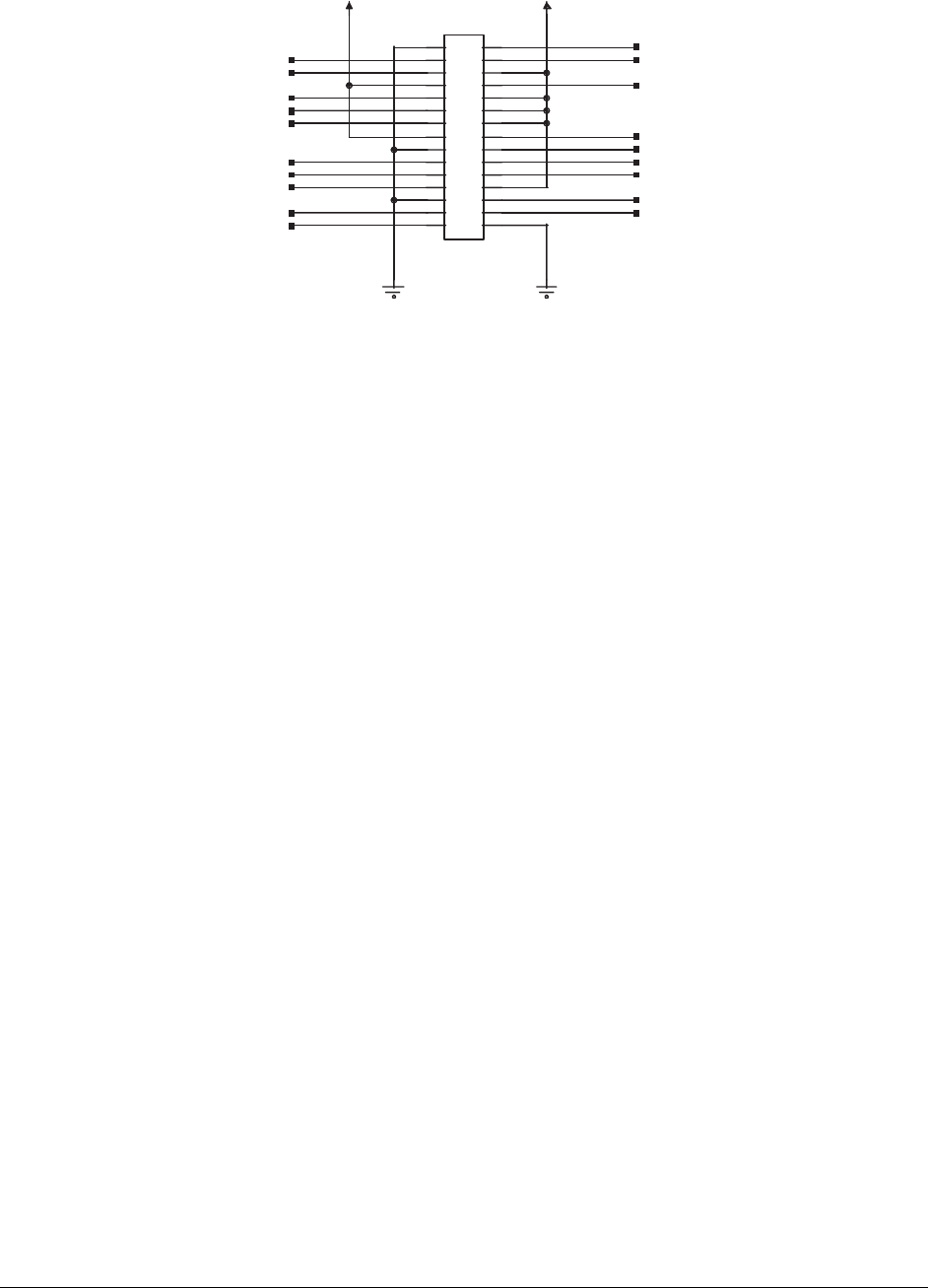

Figure 26. Mainboard Connector Signals

6.2.1 Remote On/Off (-PS_ON)

The power supply DC outputs are enabled when this signal is pulled low, below 0.8V. In the low

state the input will not source more than 1mA of current. The DC outputs are disabled when the

input is driven higher than 2.4V, or open circuited.

Provisions for de-bouncing are included in the –PS_ON circuitry. This prevents the power

supply from oscillating on and off at startup.

6.2.2 Power Good Signal (POK or P_GOOD)

A power good signal is asserted or driven high by the power supply to indicate that all outputs

are valid. If any of the outputs fails, this output is driven low.

If AC main power is lost, or if a fan has failed, this signal must be driven low at least 1ms before

any of the outputs go out of regulation.

The output is an open collector/drain. It is capable of driving the output below 0.4V with a load

of 4mA. The output has an internal pull-up resistor of 1KΩ between the output and +3.3V

stby

.

The pull-up is connected to the anode side of the +3.3V

stby

OR’ing diode.

This output also goes to I

2

C port P5.

6.2.3 VIN_GOOD

This signal is asserted, driven high, by the power supply to indicate that the input voltage meets

the minimum requirements of the input voltage range. Within 12ms after falling outside the input

voltage requirements, the output must be driven low.

The output is an open collector/drain. It is capable of driving the output below 0.4V with a load

of 4mA. The output has an internal pull-up resistor of 1KΩ between the output and +3.3V

stby

.

The pull-up is connected to the anode side of the +3.3V

stby

OR’ing diode.

This output also goes to I

2

C port P4.