Chapter 4 Signal Connections

© National Instruments Corporation 4-25 6023E/6024E/6025E User Manual

2. Using the following formula, calculate the largest possible load to

maintain a logic low level of 0.4 V and supply the maximum driving

current:

V = I × RL ⇒ RL = V/I

where:

V = 0.4 V Voltage across RL

I =46µA+10µA 4.6 V across the 100 kΩ pull-up resistor

and 10 µA maximum leakage current

Therefore:

RL =7.1kΩ ;0.4V/56µA

This resistor value, 7.1 kΩ, provides a maximum of 0.4 V on the DIO line

at power up. You can substitute smaller resistor values to lower the voltage

or to provide a margin for V

cc

variations and other factors. However,

smaller values draw more current, leaving less drive current for other

circuitry connected to this line. The 7.1 kΩ resistor reduces the amount of

logic high source current by 0.4 mA with a 2.8 V output.

Timing Specifications

♦ 6025E only

This section lists the timing specifications for handshaking with your

6025E PC<0..7> lines. The handshaking lines STB* and IBF synchronize

input transfers. The handshaking lines OBF* and ACK* synchronize

output transfers. Table 4-5 describes signals appearing in the handshaking

diagrams.

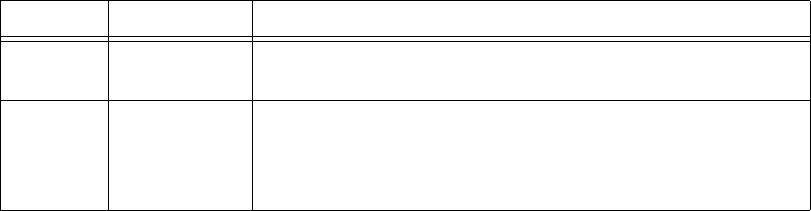

Table 4-5. Signal Names Used in Timing Diagrams

Name Type Description

STB* Input Strobe input—a low signal on this handshaking line loads data into

the input latch.

IBF Output Input buffer full—a high signal on this handshaking line indicates

that data has been loaded into the input latch. A low signal indicates

the device is ready for more data. This is an input acknowledge

signal.