INTERRUPT STRUCTURE S3C8275X/F8275X/C8278X/F8278X/C8274X/F8274X

5-10

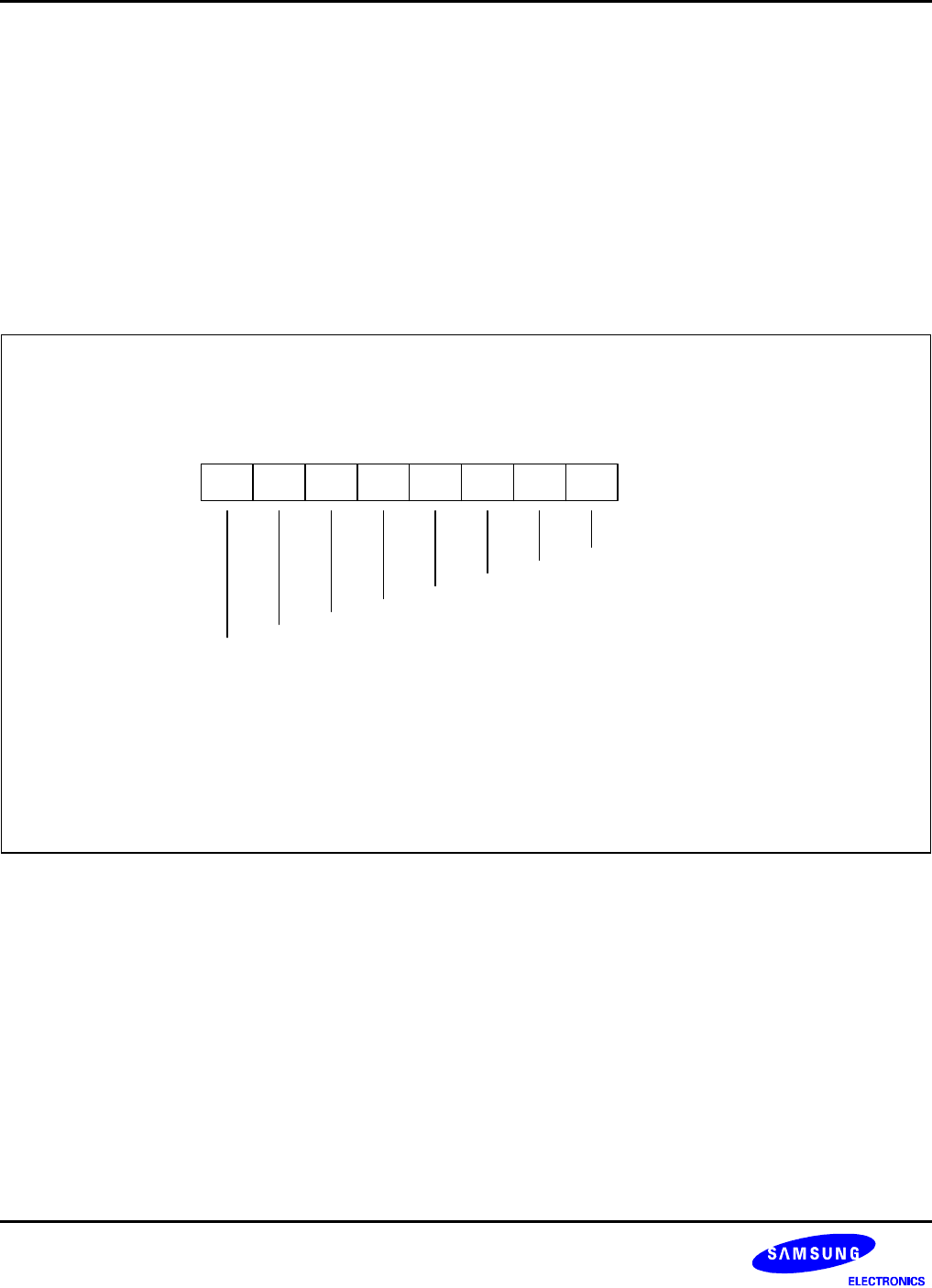

INTERRUPT MASK REGISTER (IMR)

The interrupt mask register, IMR (set 1, DDH) is used to enable or disable interrupt processing for individual

interrupt levels. After a reset, all IMR bit values are undetermined and must therefore be written to their required

settings by the initialization routine.

Each IMR bit corresponds to a specific interrupt level: bit 1 to IRQ1, bit 2 to IRQ2, and so on. When the IMR bit of

an interrupt level is cleared to "0", interrupt processing for that level is disabled (masked). When you set a level's

IMR bit to "1", interrupt processing for the level is enabled (not masked).

The IMR register is mapped to register location DDH in set 1. Bit values can be read and written by instructions

using the Register addressing mode.

Interrupt Mask Register (IMR)

DDH, Set 1, R/W

.7 .6 .5 .4 .3 .2 .1 .0MSB LSB

IRQ1

IRQ2

IRQ4

IRQ5

IRQ6

IRQ7

IRQ0

Interrupt level enable bits:

0 = Disable (mask) interrupt level

1 = Enable (un-mask) interrupt level

IRQ3

NOTE:

Before IMR register is changed to any value, all interrupts must be disable.

Using DI instruction is recommended.

Figure 5-6. Interrupt Mask Register (IMR)