Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 112 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

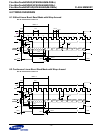

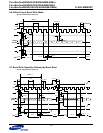

5.5 AC Characteristics for Asynchronous Read

See Timing Diagrams 6.3 and 6.4.

NOTE :

1) If OE

is disabled at the same time or before CE is disabled, the output will go to high-z by tOEZ.

If CE

is disabled at the same time or before OE is disabled, the output will go to high-z by tCEZ.

If CE

and OE are disabled at the same time, the output will go to high-z by tOEZ.

These parameters are not 100% tested.

2) This Parameter is valid at toggle bit timing in asynchronous read only. (timing diagram 6.20 and 6.21)

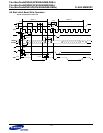

5.6 AC Characteristics for Warm Reset (RP), Hot Reset and NAND Flash Core Reset

See Timing Diagrams 6.16, 6.17 and 6.18.

NOTE :

1) These parameters are tested based on INT bit of interrupt register. Because the time on INT pin is related to the pull-up and pull-down resistor value.

2) The device may reset if tRP < tRP min(200ns), but this is not guaranteed.

Parameter Symbol

KFM4GH6Q4M/

KFN8GH6Q4M/

KFKAGH6Q4M(TBD)

Unit

Min Max

Access Time from CE

Low tCE -76ns

Asynchronous Access Time from AVD

Low tAA -76ns

Asynchronous Access Time from address valid t

ACC -76ns

Read Cycle Time t

RC 76 - ns

AVD

Low Time tAVDP 12 - ns

Address Setup to rising edge of AVD

tAAVDS 5-ns

Address Hold from rising edge of AVD

tAAVDH 6-ns

Output Enable to Output Valid t

OE -20ns

CE

Setup to AVD falling edge tCA 0-ns

CE

Disable to Output & RDY High Z

1)

tCEZ -20ns

OE

Disable to Output High Z

1)

tOEZ -15ns

AVD

High to OE Low tAVDO 0-ns

CE

Low to RDY Valid tCER -15ns

WE Disable to AVD Enable

tWEA 15 - ns

Address to OE low

tASO

2)

10 - ns

Parameter Symbol Min Max Unit

RP & Reset Command Latch to BootRAM Access

tReady1

(BufferRAM)

-5

s

RP

& Reset Command Latch(During Load Routines) to INT High (Note1)

tReady2

(NAND Flash Array)

-10

s

RP

& Reset Command Latch(During Program Routines) to INT High (Note1)

tReady2

(NAND Flash Array)

-20

s

RP

& Reset Command Latch(During Erase Routines) to INT High (Note1)

tReady2

(NAND Flash Array)

- 150

s

RP

& Reset Command Latch(NOT During Internal Routines) to INT High (Note1)

tReady2

(NAND Flash Array)

-10

s

RP

Pulse Width (Note2)

tRP

200 -

ns