Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 113 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

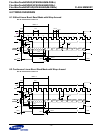

5.7 AC Characteristics for Asynchronous Write

See Timing Diagrams 6.5

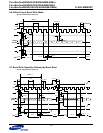

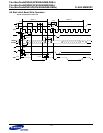

5.8 AC Characteristics for Burst Write Operation

See Timing Diagrams 6.6, 6.7 and 6.8.

NOTE :

1)Target Clock frequency is 83Mhz

Parameter Symbol Min Max Unit

WE Cycle Time tWC

70 - ns

AVD low pulse width

tAVDP

12 - ns

Address Setup Time tAAVDS

5 - ns

Address Hold Time tAAVDH

6 - ns

Data Setup Time tDS

30 - ns

Data Hold Time tDH

0 - ns

CE Setup Time

tCS

0 - ns

CE Hold Time tCH

0 - ns

WE Pulse Width tWPL

40 - ns

WE Pulse Width High tWPH

30 - ns

WE Disable to AVD Enable tWEA

15 - ns

CE Low to RDY Valid tCER

-15ns

CE Disable to Output & RDY High Z tCEZ

-20ns

Parameter Symbol

66MHz 83MHz

Unit

Min Max Min Max

Clock

CLK

1)

166183MHz

Clock Cycle

tCLK

15 - 12 - ns

AVD

Setup to CLK

tAVDS

5-4-ns

AVD

Hold Time from CLK

tAVDH

2-2-ns

Address Setup Time to CLK

tACS

5-4-ns

Address Hold Time from CLK

tACH

6-6-ns

Data Setup Time to CLK

tWDS

5-4-ns

Data Hold Time from CLK

tWDH

2-2-ns

WE

Setup Time to CLK

tWES

5-4-ns

WE

Hold Time from CLK

tWEH

6-6-ns

CLK High or Low Time

tCLKH/L

tCLK/3 - 5 - ns

CE

high pulse width

tCEHP

10 - 10 - ns

CLK to RDY Valid

tRDYO

-11- 9ns

CLK to RDY Setup Time

tRDYA

-11- 9ns

RDY Setup Time to CLK

tRDYS

4

-

3

-ns

CE

low to RDY valid

tCER

- 15 - 15 ns

Clock to CE

disable

tCEH

2tCLK-4.52tCLK-4.5 ns

CE

Setup Time to CLK

tCES

6 - 4.5 - ns

CE

Disable to Output & RDY High Z

t

CEZ

- 20 - 20 ns