Flex-MuxOneNAND4G(KFM4GH6Q4M-DEBx)

- 124 -

FLASH MEMORY

Flex-MuxOneNAND8G(KFN8GH6Q4M-DEBx)

Flex-MuxOneNAND16G(KFKAGH6Q4M-DEBx)

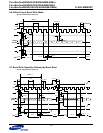

6.13 Interleave Cache Program Operation Timing

See AC Characteristics Table 5.7 and Table 5.9

1st data input 2nd data input

Address Setting

cache program Command

ADQ0~

A1, A2, An : Address of DataRAM to be written.

INT: Indicator for DataRAM’s Status (Ready=High, Busy=Low)

Ongoing Status : Indicated by OnGo bit in Controller Status Register [15] (F240h)

4KB data input : Asynch Write / Synch Write available.

Command input and INT bit or pin behavior is based on ‘INT auto mode’.

NOTE : 1) INT pin might toggle when INT bit of chip1 turns to ready before host issues ‘program’ command on chip2.

ADQ15

A1 A2

High-Z

INT bit

....

..

4KB data into

2 DataRAMs

4KB data into

2 DataRAMs

Cache program Command

program Command

Last data input

An

4KB data into

2 DataRAMs

.

Ongoing

Status

Controller Status Register Check

current : Invalid

previous: Pass=0, Fail=1

Controller Status Register Check

current : Pass=0, Fail=1

previous: Pass=0, Fail=1

...

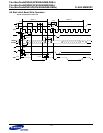

1st data input 2nd data input

Address Setting

cache program Command

ADQ0~

ADQ15

A1 A2

...

..

4KB data into

2 DataRAMs

4KB data into

2 DataRAMs

Cache program Command

program Command

Last data input

An

4KB data into

2 DataRAMs

...

Ongoing

Status

Controller Status Register Check

current : Invalid

previous: Pass=0, Fail=1

Controller Status Register Check

current : Pass=0, Fail=1

...

.....

.....

.....

Controller Status Register Check

current : Invalid (Fixed to 0)

previous: Invalid (Fixed to 0)

Controller Status Register Check

current : Invalid (Fixed to 0)

previous: Invalid (Fixed to 0)

INT bit

INT Pin

...

1)