Functional Overview

2-2 Copyright © 2006 ARM Limited. All rights reserved. ARM DDI 0389B

2.1 Functional description

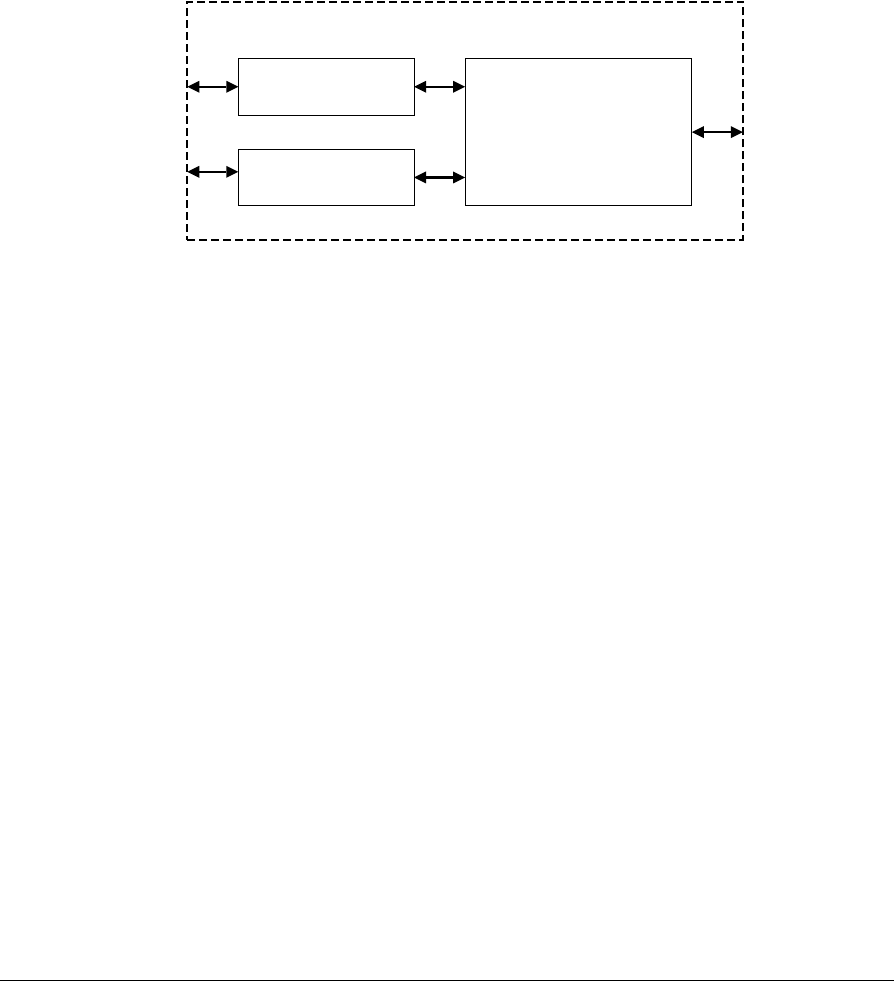

Figure 2-1 shows an AHB MC (PL241) configuration.

Figure 2-1 AHB MC (PL241) configuration

This section is divided into:

• AHB interface

• AHB to APB bridge

• Clock domains on page 2-3

• Low-power interface on page 2-3

• SMC on page 2-4.

2.1.1 AHB interface

The AHB MC fully supports the AMBA AHB 2.0 specification. This interface

component converts the incoming AHB transfers to the required transfers of the internal

interconnect protocol. Because of the design of the internal interconnect, some

optimizations are made in the interface to improve performance.

See AHB interface operation on page 2-7 for more information.

2.1.2 AHB to APB bridge

The internal memory controllers of the AHB MC use the AMBA3 APB protocol for

their configuration ports. To enable the AHB MC to externally function as an AHB

device, the APB configuration ports are connected to an AHB to APB bridge. The

bridge converts incoming AHB transfers from the configuration port to the APB

transfers that the internal memory controller requires. This bridge is part of the

PrimeCell infrastructure components, part BP127.

See AHB to APB bridge operation on page 2-10 for more information.

$+%LQWHUIDFH

60&

$+%0&3/

$+%WR$3%

EULGJH

$+%

ELW65$0125

IRXUFKLSV

$3%6

$+%

FRQILJXUDWLRQ

SRUW

60

0