Programmer’s Model

ARM DDI 0389B Copyright © 2006 ARM Limited. All rights reserved. 3-11

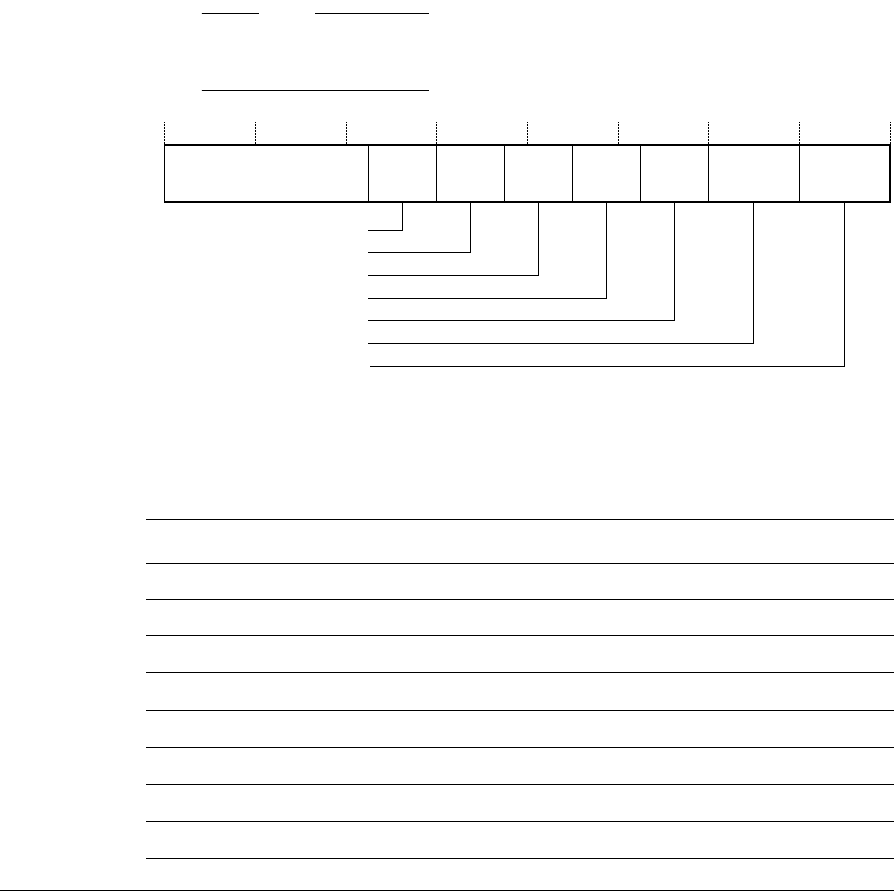

3.3.6 SMC Set Cycles Register at 0x1014

This is the holding register for the smc_set_cycles0_<n>. The write-only

smc_set_cycles Register enables the time interval to be set for holding registers before

data can be written to the memory manager specific registers. This register cannot be

written to in either the Reset or Low-power state. Figure 3-11 shows the register bit

assignments.

Note

Table 3-7 describes register holding, see Memory manager operation on page 2-22 for

more information.

Figure 3-11 smc_set_cycles Register bit assignments

Table 3-7 lists the register bit assignments.

6HWBW

6HWBW

6HWBW

6HWBW

6HWBW

6HWBW

6HWBW

8QGHILQHG

Table 3-7 smc_set_cycles Register bit assignments

Bits Name Function

[31:23] - Reserved, undefined. Write as zero.

[22:20] Set_t6 Reserved.

[19:17] Set_t5 Holding register for value to be written to the specific chip Register t

TR

field.

[16:14] Set_t4 Holding register for value to be written to the specific chip Register t

PC

field.

[13:11] Set_t3 Holding register for value to be written to the specific chip Register t

WP

field.

[10:8] Set_t2 Holding register for value to be written to the specific chip Register t

CEOE

field.

[7:4] Set_t1 Holding register for value to be written to the specific chip Register t

WC

field.

[3:0] Set_t0 Holding register for value to be written to the specific chip Register t

RC

field.