Programmer’s Model

ARM DDI 0389B Copyright © 2006 ARM Limited. All rights reserved. 3-9

Table 3-4 lists the register bit assignments.

3.3.4 SMC Clear Configuration Register at 0x100C

The write-only smc_memc_cfg_clr Register enables the memory controller to be

moved out of the Low-power state, and the interrupts disabled. This register cannot be

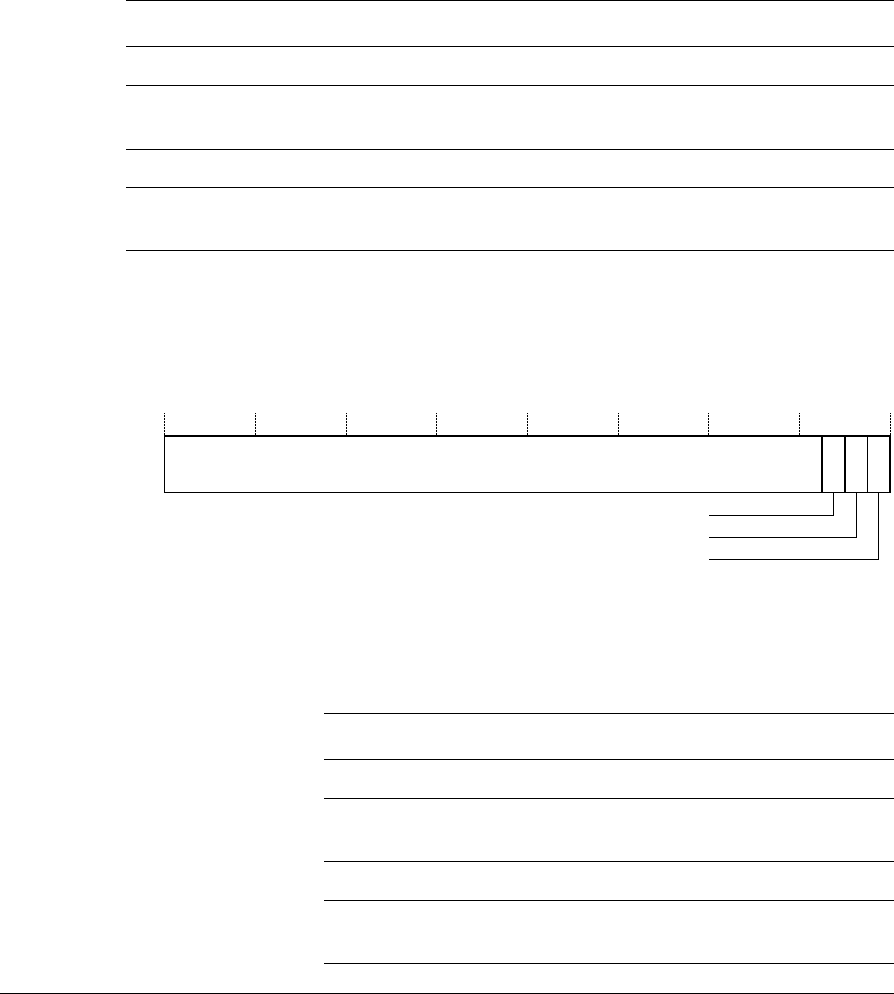

written to in the Reset state. Figure 3-9 shows the register bit assignments.

Figure 3-9 smc_memc_cfg_clr Register bit assignments

Table 3-5 lists the register bit assignments.

Table 3-4 smc_memc_cfg_set Register bit assignments

Bits Name Function

[31:3] - Reserved, undefined. Write as zero.

[2] low_power_req b0 = no effect

b1 = request the SMC to enter Low-power state when it next becomes idle.

[1] - Reserved, undefined. Write as zero.

[0] int_enable0 b0 = no effect

b1 = interrupt enable, memory interface 0.

LQWBGLVDEOH

5HVHUYHG

ORZBSRZHUBH[LW

8QGHILQHG

Table 3-5 smc_memc_cfg_clr Register bit assignments

Bits Name Function

[31:3] - Reserved, undefined. Write as zero.

[2] low_power_exit b0 = no effect

b1 = request the SMC to exit Low-power state.

[1] - Reserved, undefined. Write as zero.

[0] int_disable0 b0 = no effect

b1 = interrupt disable, memory interface 0.