Programmer’s Model

3-10 Copyright © 2006 ARM Limited. All rights reserved. ARM DDI 0389B

3.3.5 SMC Direct Command Register at 0x1010

The write-only smc_direct_cmd Register passes commands to the external memory, and

controls the updating of the chip configuration registers with values held in the

set_opmode and set_cycles registers.

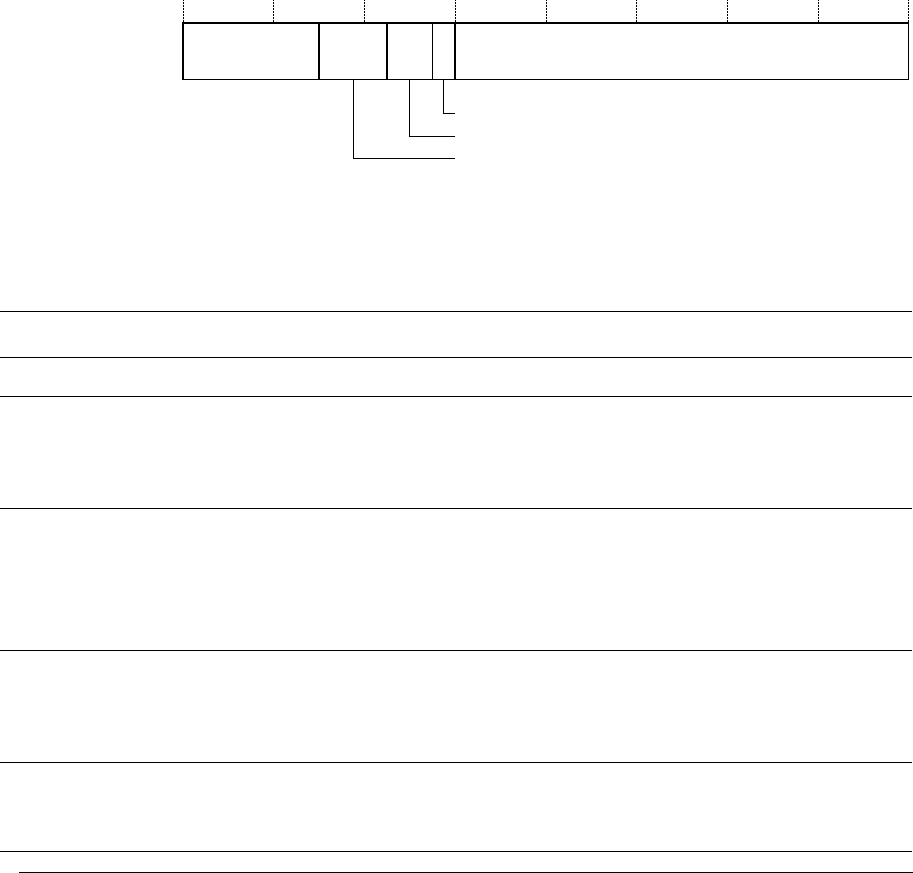

This register cannot be written to in either the Reset or Low-power state. Figure 3-10

shows the register bit assignments.

Figure 3-10 smc_direct_cmd Register bit assignments

Table 3-6 lists the register bit assignments.

VHWBFUH

$GGU

8QGHILQHG

FPGBW\SH

FKLSBVHOHFW

Table 3-6 smc_direct_cmd Register bit assignments

Bits Name Function

[31:26] - Reserved, undefined. Write as zero.

[25:23] chip_select Selects chip configuration register bank to update and enables chip mode register access depending

on cmd_type. The encoding is:

b000-b011 = chip selects 1-4 on interface 0

b100-b111 = reserved.

[22:21] cmd_type Determines the current command. The encoding is:

b00 = UpdateRegs and AHB command

b01 = ModeReg access

b10 = UpdateRegs

b11 = ModeReg and UpdateRegs.

[20] set_cre Maps to configuration register enable, smc_cre, output, when a ModeReg command is issued. The

encoding is:

b0 = smc_cre is LOW

b1 = smc_cre is HIGH when ModeReg write occurs.

[19:0] addr Bits mapped to external memory address bits [19:0] when command is ModeReg access.

Addr[19:16] are undefined.

Addr[15:0] matches wdata[15:0] when the commands are UpdateRegs and AHB command access.