EMAC Module Registers

www.ti.com

5.23 Receive Unicast Clear Register (RXUNICASTCLEAR)

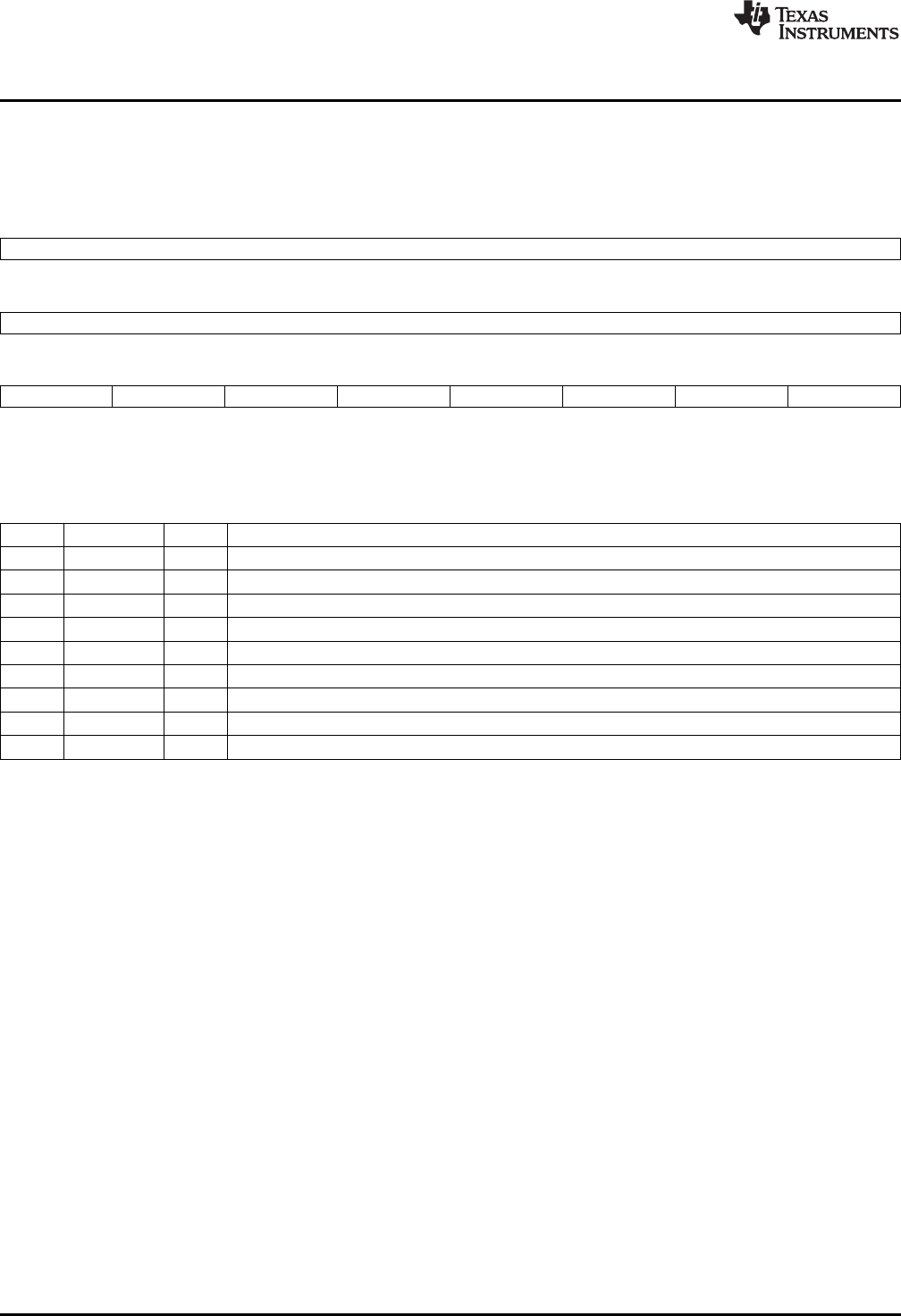

The receive unicast clear register (RXUNICASTCLEAR) is shown in Figure 61 and described in Table 60.

Figure 61. Receive Unicast Clear Register (RXUNICASTCLEAR)

31 16

Reserved

R-0

15 8

Reserved

R-0

7 6 5 4 3 2 1 0

RXCH7EN RXCH6EN RXCH5EN RXCH4EN RXCH3EN RXCH2EN RXCH1EN RXCH0EN

R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0 R/W1C-0

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing a 0 has no effect); -n = value after reset

Table 60. Receive Unicast Clear Register (RXUNICASTCLEAR) Field Descriptions

Bit Field Value Description

31-8 Reserved 0 Reserved

7 RXCH7EN 0-1 Receive channel 7 unicast enable clear bit. Write 1 to clear the enable, a write of 0 has no effect.

6 RXCH6EN 0-1 Receive channel 6 unicast enable clear bit. Write 1 to clear the enable, a write of 0 has no effect.

5 RXCH5EN 0-1 Receive channel 5 unicast enable clear bit. Write 1 to clear the enable, a write of 0 has no effect.

4 RXCH4EN 0-1 Receive channel 4 unicast enable clear bit. Write 1 to clear the enable, a write of 0 has no effect.

3 RXCH3EN 0-1 Receive channel 3 unicast enable clear bit. Write 1 to clear the enable, a write of 0 has no effect.

2 RXCH2EN 0-1 Receive channel 2 unicast enable clear bit. Write 1 to clear the enable, a write of 0 has no effect.

1 RXCH1EN 0-1 Receive channel 1 unicast enable clear bit. Write 1 to clear the enable, a write of 0 has no effect.

0 RXCH0EN 0-1 Receive channel 0 unicast enable clear bit. Write 1 to clear the enable, a write of 0 has no effect.

106

EMAC/MDIO Module SPRUFL5B–April 2011

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated