Arbiter and

bus switches

CPU

DMA Controllers

8K byte

descriptor

memory

Configuration

registers

Interrupt

logic

Interrupts

to CPU

EMAC interrupts

MDIO interrupts

Configuration bus

Transmit and Receive

www.ti.com

Architecture

2.6 EMAC Control Module

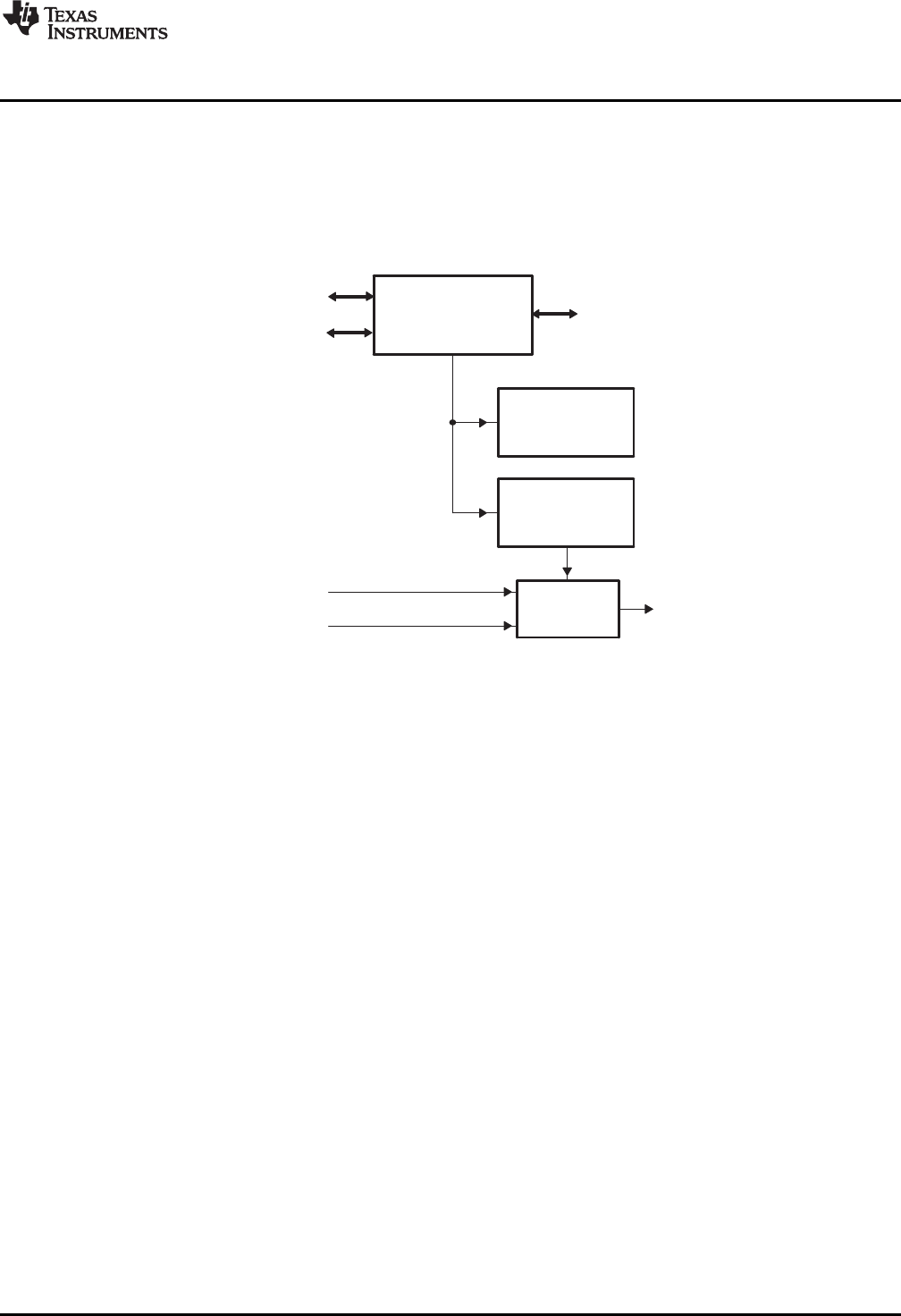

The EMAC control module (Figure 9) interfaces the EMAC and MDIO modules to the rest of the system,

and also provides a local memory space to hold EMAC packet buffer descriptors. Local memory is used to

help avoid contention with device memory spaces. Other functions include the bus arbiter, and interrupt

logic control.

Figure 9. EMAC Control Module Block Diagram

2.6.1 Internal Memory

The EMAC control module includes 8K bytes of internal memory (CPPI buffer descriptor memory). The

internal memory block is essential for allowing the EMAC to operate more independently of the CPU. It

also prevents memory underflow conditions when the EMAC issues read or write requests to descriptor

memory. (Memory accesses to read or write the actual Ethernet packet data are protected by the EMAC's

internal FIFOs).

A descriptor is a 16-byte memory structure that holds information about a single Ethernet packet buffer,

which may contain a full or partial Ethernet packet. Thus with the 8K memory block provided for descriptor

storage, the EMAC module can send and received up to a combined 512 packets before it needs to be

serviced by application or driver software.

2.6.2 Bus Arbiter

The EMAC control module bus arbiter operates transparently to the rest of the system. It is used:

• To arbitrate between the CPU and EMAC buses for access to internal descriptor memory.

• To arbitrate between internal EMAC buses for access to system memory.

29

SPRUFL5B–April 2011 EMAC/MDIO Module

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated