EMAC Module Registers

www.ti.com

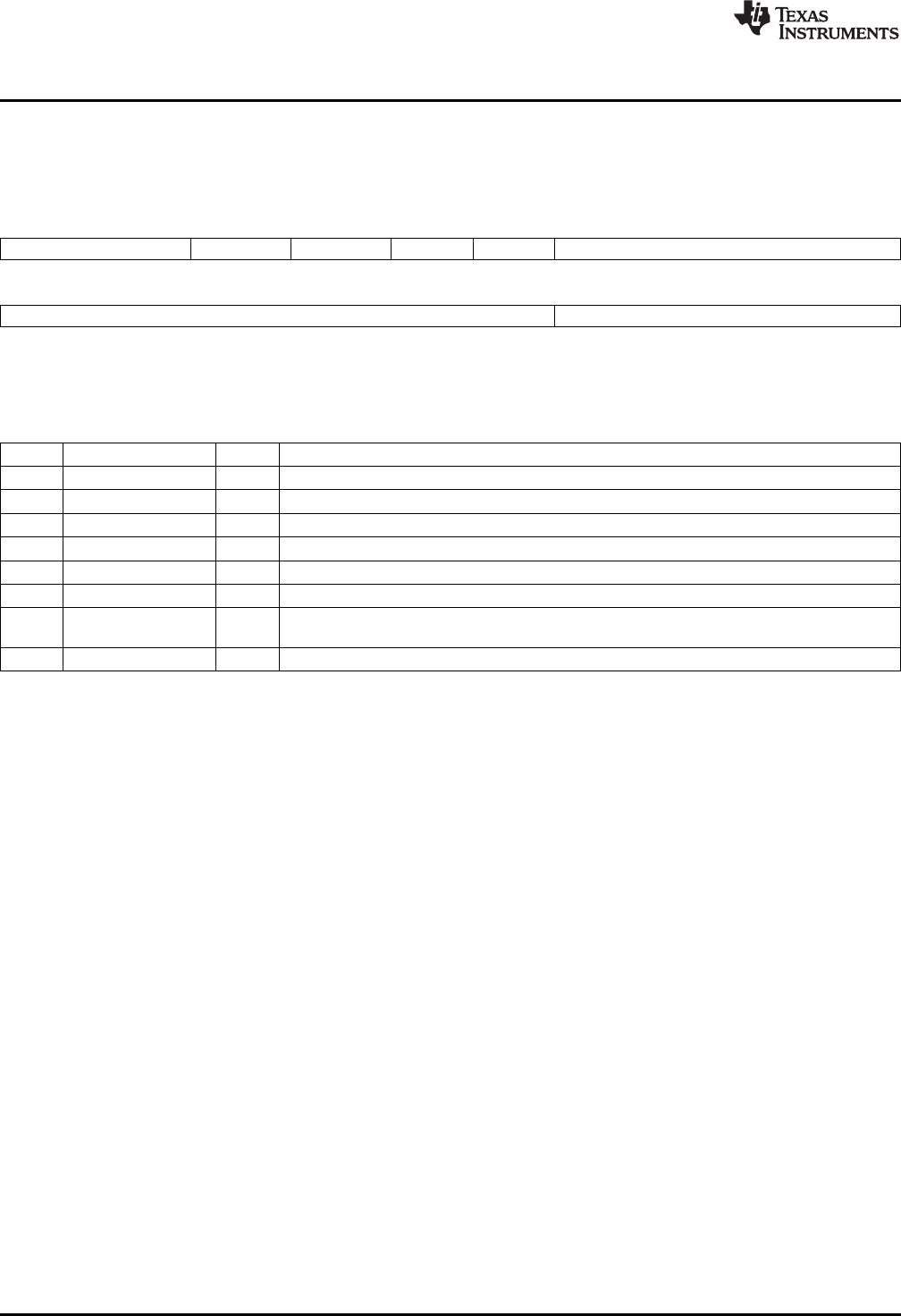

5.11 MAC Input Vector Register (MACINVECTOR)

The MAC input vector register (MACINVECTOR) is shown in Figure 49 and described in Table 48.

Figure 49. MAC Input Vector Register (MACINVECTOR)

31 28 27 26 25 24 23 16

Reserved STATPEND HOSTPEND LINKINT0 USERINT0 TXPEND

R-0 R-0 R-0 R-0 R-0 R-0

15 8 7 0

RXTHRESHPEND RXPEND

R-0 R-0

LEGEND: R = Read only; -n = value after reset

Table 48. MAC Input Vector Register (MACINVECTOR) Field Descriptions

Bit Field Value Description

31-28 Reserved 0 Reserved

27 STATPEND 0-1 EMAC module statistics interrupt (STATPEND) pending status bit

26 HOSTPEND 0-1 EMAC module host error interrupt (HOSTPEND) pending status bit

25 LINKINT0 0-1 MDIO module USERPHYSEL0 (LINKINT0) status bit

24 USERINT0 0-1 MDIO module USERACCESS0 (USERINT0) status bit

23-16 TXPEND 0-FFh Transmit channels 0-7 interrupt (TXnPEND) pending status. Bit 16 is TX0PEND.

15-8 RXTHRESHPEND 0-FFh Receive channels 0-7 interrupt (RXnTHRESHPEND) pending status. Bit 8 is

RX0THRESHPEND.

7-0 RXPEND 0-FFh Receive channels 0-7 interrupt (RXnPEND) pending status bit. Bit 0 is RX0PEND.

94

EMAC/MDIO Module SPRUFL5B–April 2011

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated