www.ti.com

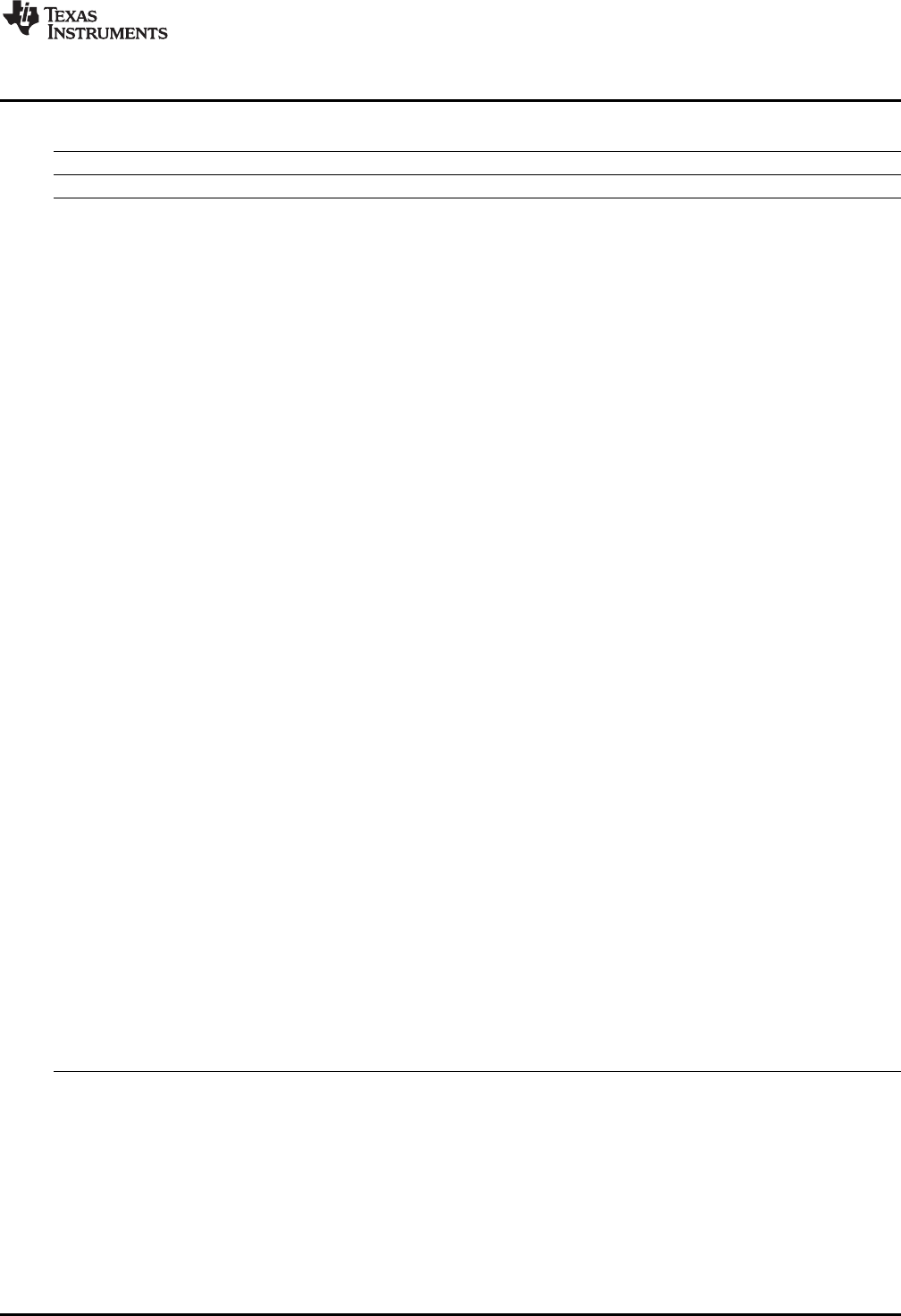

EMAC Module Registers

Table 37. Ethernet Media Access Controller (EMAC) Registers (continued)

Offset Acronym Register Description Section

67Ch RX7CP Receive Channel 7 Completion Pointer Register Section 5.49

Network Statistics Registers

200h RXGOODFRAMES Good Receive Frames Register Section 5.50.1

204h RXBCASTFRAMES Broadcast Receive Frames Register Section 5.50.2

208h RXMCASTFRAMES Multicast Receive Frames Register Section 5.50.3

20Ch RXPAUSEFRAMES Pause Receive Frames Register Section 5.50.4

210h RXCRCERRORS Receive CRC Errors Register Section 5.50.5

214h RXALIGNCODEERRORS Receive Alignment/Code Errors Register Section 5.50.6

218h RXOVERSIZED Receive Oversized Frames Register Section 5.50.7

21Ch RXJABBER Receive Jabber Frames Register Section 5.50.8

220h RXUNDERSIZED Receive Undersized Frames Register Section 5.50.9

224h RXFRAGMENTS Receive Frame Fragments Register Section 5.50.10

228h RXFILTERED Filtered Receive Frames Register Section 5.50.11

22Ch RXQOSFILTERED Receive QOS Filtered Frames Register Section 5.50.12

230h RXOCTETS Receive Octet Frames Register Section 5.50.13

234h TXGOODFRAMES Good Transmit Frames Register Section 5.50.14

238h TXBCASTFRAMES Broadcast Transmit Frames Register Section 5.50.15

23Ch TXMCASTFRAMES Multicast Transmit Frames Register Section 5.50.16

240h TXPAUSEFRAMES Pause Transmit Frames Register Section 5.50.17

244h TXDEFERRED Deferred Transmit Frames Register Section 5.50.18

248h TXCOLLISION Transmit Collision Frames Register Section 5.50.19

24Ch TXSINGLECOLL Transmit Single Collision Frames Register Section 5.50.20

250h TXMULTICOLL Transmit Multiple Collision Frames Register Section 5.50.21

254h TXEXCESSIVECOLL Transmit Excessive Collision Frames Register Section 5.50.22

258h TXLATECOLL Transmit Late Collision Frames Register Section 5.50.23

25Ch TXUNDERRUN Transmit Underrun Error Register Section 5.50.24

260h TXCARRIERSENSE Transmit Carrier Sense Errors Register Section 5.50.25

264h TXOCTETS Transmit Octet Frames Register Section 5.50.26

268h FRAME64 Transmit and Receive 64 Octet Frames Register Section 5.50.27

26Ch FRAME65T127 Transmit and Receive 65 to 127 Octet Frames Register Section 5.50.28

270h FRAME128T255 Transmit and Receive 128 to 255 Octet Frames Register Section 5.50.29

274h FRAME256T511 Transmit and Receive 256 to 511 Octet Frames Register Section 5.50.30

278h FRAME512T1023 Transmit and Receive 512 to 1023 Octet Frames Register Section 5.50.31

27Ch FRAME1024TUP Transmit and Receive 1024 to RXMAXLEN Octet Frames Register Section 5.50.32

280h NETOCTETS Network Octet Frames Register Section 5.50.33

284h RXSOFOVERRUNS Receive FIFO or DMA Start of Frame Overruns Register Section 5.50.34

288h RXMOFOVERRUNS Receive FIFO or DMA Middle of Frame Overruns Register Section 5.50.35

28Ch RXDMAOVERRUNS Receive DMA Overruns Register Section 5.50.36

85

SPRUFL5B–April 2011 EMAC/MDIO Module

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated