EMAC Module Registers

www.ti.com

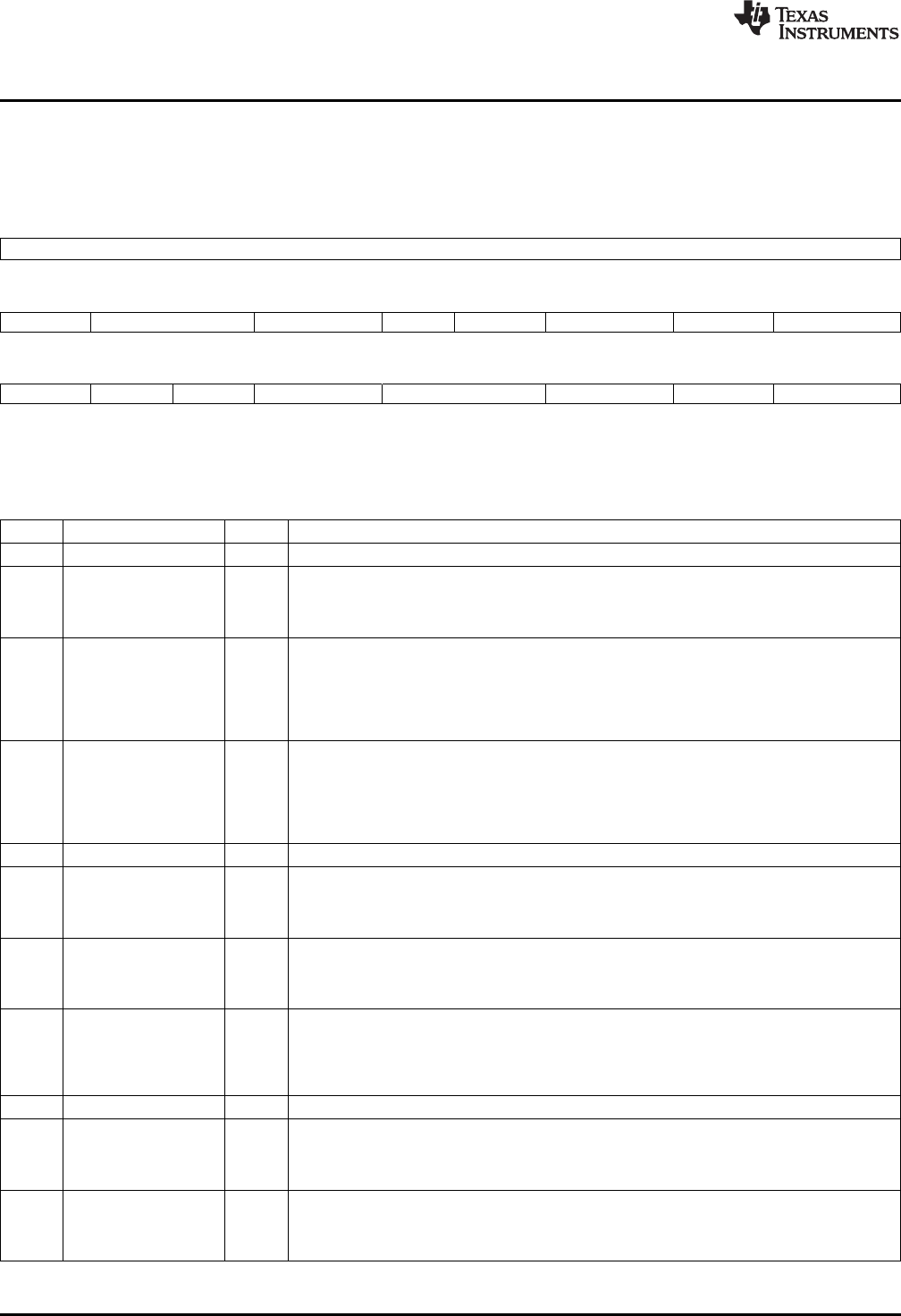

5.29 MAC Control Register (MACCONTROL)

The MAC control register (MACCONTROL) is shown in Figure 67 and described in Table 66.

Figure 67. MAC Control Register (MACCONTROL)

31 16

Reserved

R-0

15 14 13 12 11 10 9 8

RMIISPEED RXOFFLENBLOCK RXOWNERSHIP Rsvd CMDIDLE TXSHORTGAPEN TXPTYPE Reserved

R/W-0 R/W-0 R/W-0 R-0 R/W-0 R/W-0 R/W-0 R-0

7 6 5 4 3 2 1 0

Reserved TXPACE GMIIEN TXFLOWEN RXBUFFERFLOWEN Reserved LOOPBACK FULLDUPLEX

R-0 R/W-0 R/W-0 R/W-0 R/W-0 R-0 R/W-0 R/W-0

LEGEND: R/W = Read/Write; R = Read only; -n = value after reset

Table 66. MAC Control Register (MACCONTROL) Field Descriptions

Bit Field Value Description

31-16 Reserved 0 Reserved

15 RMIISPEED RMII interface transmit and receive speed select.

0 Operate RMII interface in 10 Mbps speed mode.

1 Operate RMII interface in 100 Mbps speed mode.

14 RXOFFLENBLOCK Receive offset / length word write block.

0 Do not block the DMA writes to the receive buffer descriptor offset / buffer length word.

1 Block all EMAC DMA controller writes to the receive buffer descriptor offset / buffer length

words during packet processing. When this bit is set, the EMAC will never write the third word

to any receive buffer descriptor.

13 RXOWNERSHIP Receive ownership write bit value.

0 The EMAC writes the Receive ownership bit to 0 at the end of packet processing.

1 The EMAC writes the Receive ownership bit to 1 at the end of packet processing. If you do not

use the ownership mechanism, you can set this mode to preclude the necessity of software

having to set this bit each time the buffer descriptor is used.

12 Reserved 0 Reserved

11 CMDIDLE Command Idle bit

0 Idle is not commanded.

1 Idle is commanded (read IDLE in the MACSTATUS register).

10 TXSHORTGAPEN Transmit Short Gap Enable

0 Transmit with a short IPG is disabled. Normal 96-bit time IPG is inserted between packets.

1 Transmit with a short IPG is enabled. Shorter 88-bit time IPG is inserted between packets.

9 TXPTYPE Transmit queue priority type

0 The queue uses a round-robin scheme to select the next channel for transmission.

1 The queue uses a fixed-priority (channel 7 highest priority) scheme to select the next channel

for transmission.

8-7 Reserved 0 Reserved

6 TXPACE Transmit pacing enable bit

0 Transmit pacing is disabled.

1 Transmit pacing is enabled.

5 GMIIEN GMII enable bit

0 GMII RX and TX are held in reset.

1 GMII RX and TX are enabled for receive and transmit.

110

EMAC/MDIO Module SPRUFL5B–April 2011

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated