DMA

Master

8KCPPI

RAM

Interrupt

Combiner

C0

C1

C2

ControlModule

EMAC

Module

MDIO

Module

EMAC

Interrupts

MDIO

Interrupts

Interrupts

EMACSubSystem

RegisterBus

DMA Bus

MII/RMIIBus

MDIOBus

www.ti.com

Introduction

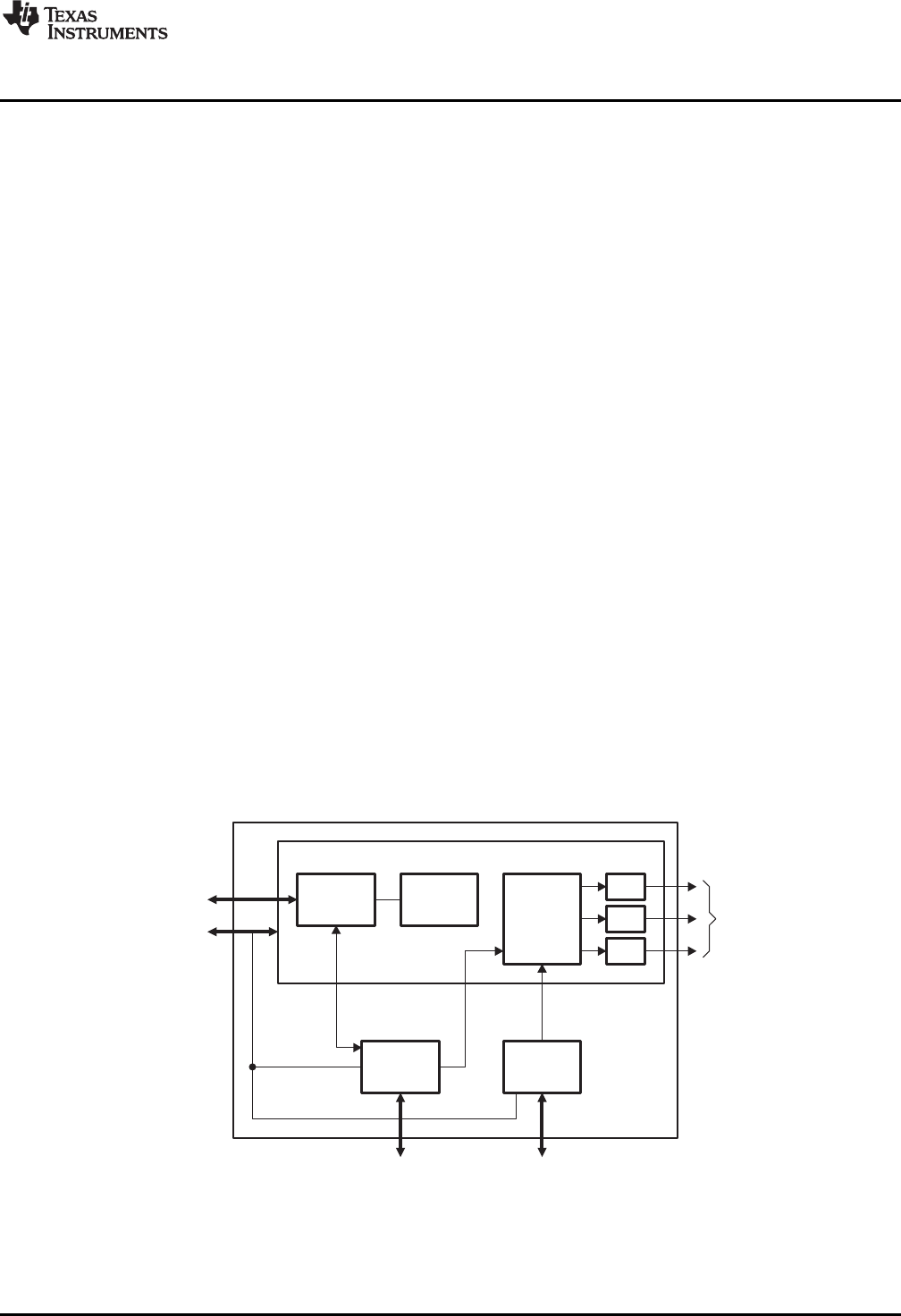

1.3 Functional Block Diagram

Figure 1 shows the three main functional modules of the EMAC/MDIO peripheral:

• EMAC control module

• EMAC module

• MDIO module

The EMAC control module is the main interface between the device core processor to the EMAC and

MDIO modules. The EMAC control module controls device interrupts and incorporates an 8k-byte internal

RAM to hold EMAC buffer descriptors (also known as CPPI RAM).

The MDIO module implements the 802.3 serial management interface to interrogate and control up to 32

Ethernet PHYs connected to the device by using a shared two-wire bus. Host software uses the MDIO

module to configure the autonegotiation parameters of each PHY attached to the EMAC, retrieve the

negotiation results, and configure required parameters in the EMAC module for correct operation. The

module is designed to allow almost transparent operation of the MDIO interface, with very little

maintenance from the core processor.

The EMAC module provides an efficient interface between the processor and the network. The EMAC on

this device supports 10Base-T (10 Mbits/sec) and 100BaseTX (100 Mbits/sec), half-duplex and full-duplex

mode, and hardware flow control and quality-of-service (QOS) support.

Figure 1 shows the main interface between the EMAC control module and the CPU. The following

connections are made to the device core:

• The DMA bus connection from the EMAC control module allows the EMAC module to read and write

both internal and external memory through the DMA memory transfer controller.

• The EMAC control, EMAC, and MDIO modules all have control registers. These registers are

memory-mapped into device memory space via the device configuration bus. Along with these

registers, the control module’s internal CPPI RAM is mapped into this same range.

• The EMAC and MDIO interrupts are combined into four interrupt signals within the control module.

Three configurable interrupt cores within the control module receive all four interrupt signals from the

combiner and submit interrupt requests to the CPU.

Figure 1. EMAC and MDIO Block Diagram

13

SPRUFL5B–April 2011 EMAC/MDIO Module

Submit Documentation Feedback

© 2011, Texas Instruments Incorporated