86 Software Developer’s Manual

PCI Local Bus Interface

As a target, the Ethernet controller only accepts transactions that address its BARs or a

configuration transaction in which its IDSEL input is asserted. In PCI-X mode, the Ethernet

controller also accepts split completion for an outstanding memory read command that it has

requested. The Ethernet controller does not respond to Interrupt Acknowledge or Special Cycle in

either mode.

As a master, the Ethernet controller generates Read and Write commands for different causes as

listed in Table 4-7. The addresses of these transactions are programmed either by system software

or the software driver. The Ethernet controller always expects that they are claimed by one of the

devices on the bus segment. The Ethernet controller never generates Interrupt Acknowledge,

Special Cycle, I/O commands, or Configuration Commands.

Transaction burst length on PCI is determined by several factors, including the PCI latency timer

expiration, the type of bus transfer (descriptor read/write or data read/write) made, the size of the

data transfer (for data transfers), and whether the cycle is initiated by the receive or transmit logic.

Dh Dual Address Cycle DAC Dual Address Cycle DAC

Eh Memory Read Line MRL Memory Read Block MRB

Fh Memory Write & Invalidate MWI Memory Write Block MWB

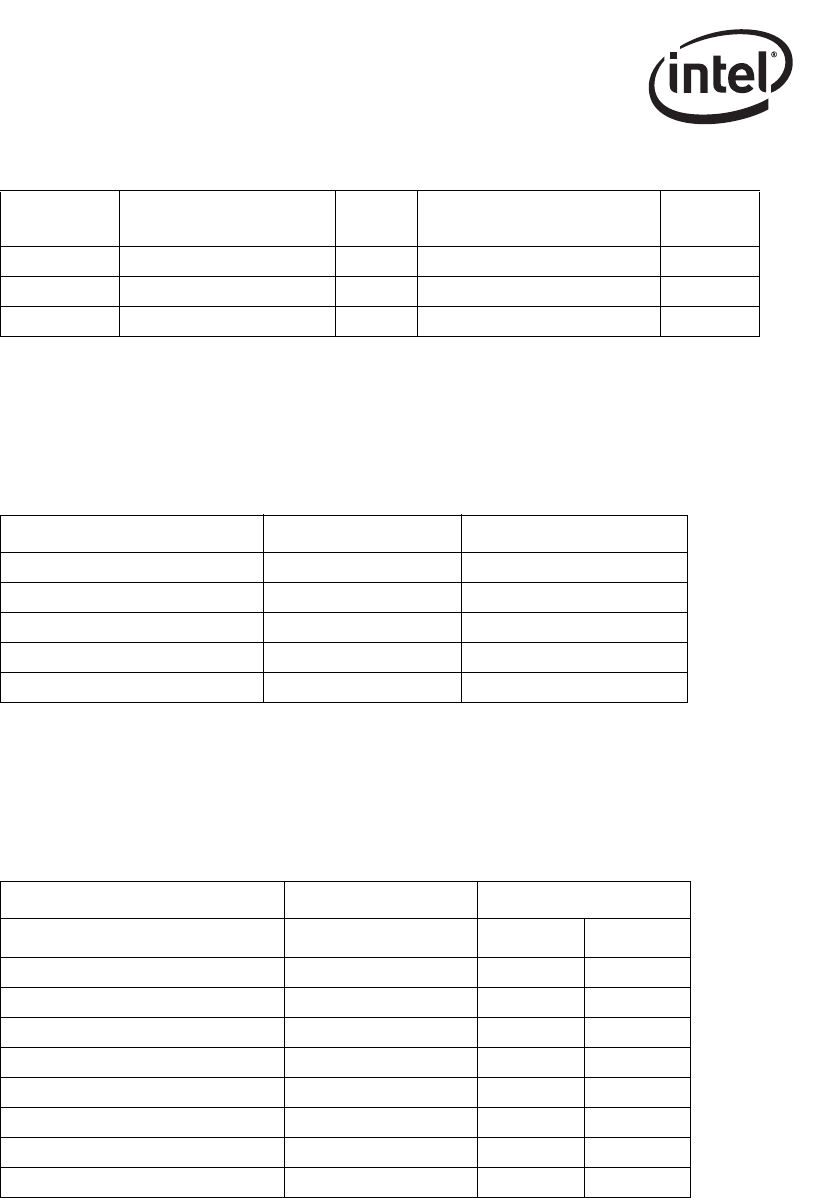

Table 4-5. PCI and PCI-X Encoding Difference

C/BE

Encoding

PCI Commands Abr. PCI-X Commands Abr.

Table 4-6. Accepted PCI/PCI-X Command as a Target

Transaction Target PCI Commands PCI-X Commands

Register or Flash Read MR,MRL,MRM,IOR MRD, MRB, AMR,IOR

Register or Flash Write MW, MWI,IOW MW, MWB, AMW,IOW

Configuration Read CFR CFR

Configuration Write CFW CFW

Memory Read Completion N/A SC

Table 4-7. Generated PCI/PCI-X as a Master

Transaction Cause PCI Commands PCI-X Commands

CMD RO

Tx Descriptor Read MR,MRL,MRM MRB 1

Tx Descriptor Write back MW,MWI MWB 0

Tx Data Read MR, MRL,MRM MRB 1

Rx Descriptor Read MR,MRL,MRM MRB 1

Rx Descriptor Write back MW,MWI MWB 0

Rx Data Write MW,MWI MWB 1

Message Signaled Interrupt

a

MW MWB 0

Split Completion N/A SC N/A

a. Not applicable to the 82541xx or 82547GI/EI.