300 Software Developer’s Manual

Register Descriptions

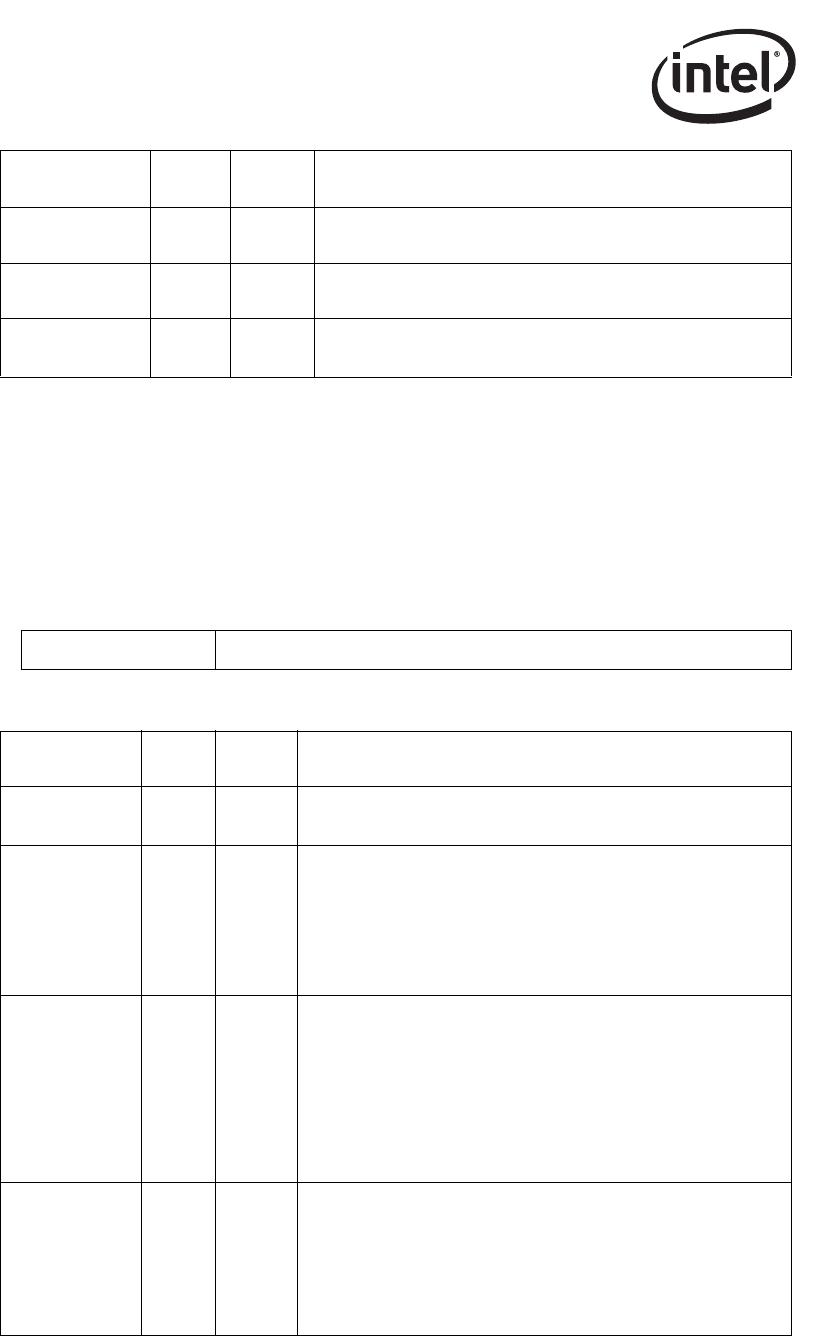

13.4.22 Receive Control Register

RCTL (00100h; R/W)

This register controls all Ethernet controller receiver functions.

Table 13-67. RCTL Register Bit Description

TXD_LOW 15 X

Clears the mask for Transmit Descriptor Low Threshold hit (not

applicable to the 82544GC/EI).

SRPD 16 X

Clears mask for Small Receive Packet Detect Interrupt (not

applicable to the 82544GC/EI).

Reserved 31:17 X

Reserved

Should be written with 1b to ensure future compatibility.

Field Bit(s)

Initial

Value

Description

31 27 26 0

Reserved Receive Control Bits

Field Bit(s)

Initial

Value

Description

Reserved 0 0b

Reserved

Write to 0b for future compatibility.

EN 1 0b

Receiver Enable

The receiver is enabled when this bit is 1b. Writing this bit to 0b

stops reception after receipt of any in-progress packets. Data

remains in the receive FIFO until the device is re–enabled.

Disabling or re-enabling the receiver does not reinitialize the packet

filter logic that demarcates packet start and end locations in the

FIFO; Therefore the receiver must be reset before re-enabling it.

SBP 2 0b

Store Bad Packets

0b = do not store.

1b = store bad packets.

When set, the Ethernet controller stores bad packets (CRC error,

symbol error, sequence error, length error, alignment error, short

packets or where carrier extension or RX_ERR errors) that pass the

filter function in host memory. When the Ethernet controller is in

promiscuous mode, and SBP is set, it might possibly store all

packets.

UPE 3 0b

Unicast Promiscuous Enabled

0b = Disabled.

1b = Enabled.

When set, passes without filtering out all received unicast packets.

Otherwise, the Ethernet controller accepts or rejects unicast

packets based on the received packet destination address match

with 1 of the 16 stored addresses.