Software Developer’s Manual 75

PCI Local Bus Interface

Expansion ROM Base Address

This register is used to define the address and size information for boot-

time access to the optional Flash memory.

CardBus CIS Pointer (82541PI/GI/EI and 82540EP Only)

When the Enable CLK_RUN# bit of the EEPROM’s Initialization Control

Word 2 and the 64/32 BAR bit of the EEPROM Initialization Control

Word 1 (indicating a 32-bit BAR) are both set to 1b, the Cardbus CIS

Pointer contains a value of 00000022h. Otherwise, it contains a value of

00000000h.

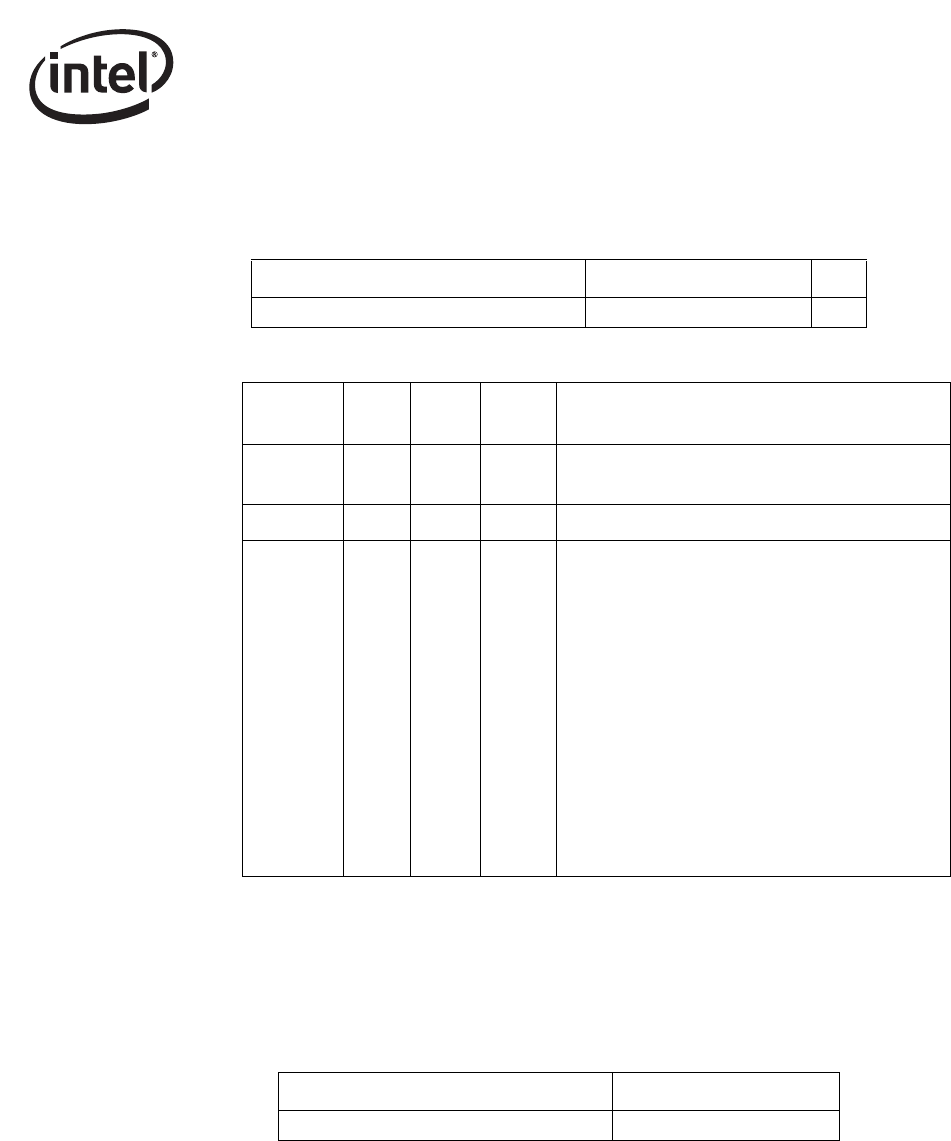

31 11 10 1 0

Expansion Rom Base Address Reserved En

Field Bit(s)

Read/

Write

Initial

Value

Description

En 0 R/W 0b

1b = Enables expansion ROM access.

0b = Disables expansion ROM access.

Reserved 10:1 R 0b Always read as 0b. Writes are ignored.

Address 31:11 R/W 0b

The lower bits of the address are hard-wired to 0b.

The upper bits can be written by the system software

to set the base address of the register or flash

address space.

Since the flash is used as the expansion ROM, the

size of the expansion ROM can very between 64 KB

and 512 KB, depending on the FLASH size read

from the EEPROM.

Flash Size Valid Bits Zero Bits:

• 64 KB 63/31:16 15:11

• 128 KB 63/31:17 16:11

• 256 KB 63/31:18 17:11

• 512 KB 63/31:19 18:11

31 3 2 0

Offset Space