Receive and Transmit Description

Software Developer’s Manual 39

Notes:

1. VLE, IFCS, and IC are qualified by EOP. That is, hardware interprets these bits ONLY when

EOP is set.

2. Hardware only sets the DD bit for descriptors with RS set.

3. Descriptors with the null address (0b) or zero length transfer no data. If they have the RS bit

set then the DD field in the status word is written when hardware processes them.

4. Although the transmit interrupt may be delayed, the descriptor write-back requested by setting

the RS bit is performed without delay unless descriptor write-back bursting is enabled.

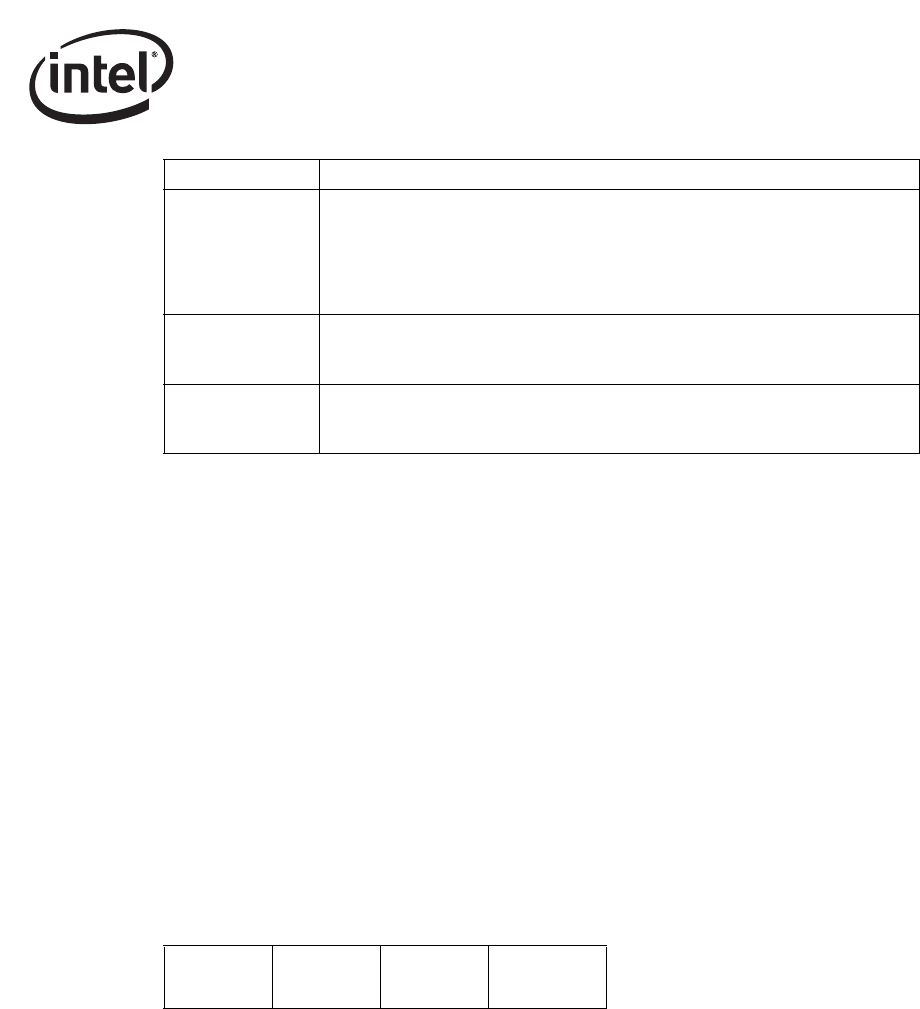

3.3.3.2 Transmit Descriptor Status Field Format

The STATUS field stores the applicable transmit descriptor status and has the fields shown in Table

3-11.

The transmit descriptor status field is only present in cases where RS (or RPS for the 82544GC/EI

only) is set in the command field.

Table 3-11. Transmit Status Layout

IC (bit 2)

Insert Checksum

When set, the Ethernet controller needs to insert a checksum at the offset indicated

by the CSO field. The checksum calculations are performed for the entire packet

starting at the byte indicated by the CCS field. IC is ignored if CSO and CCS are out

of the packet range. This occurs when (CSS length) OR (CSO length - 1). IC is

valid only when EOP is set.

IFCS (bit 1)

Insert FCS

Controls the insertion of the FCS/CRC field in normal Ethernet packets. IFCS is

valid only when EOP is set.

EOP (bit 0)

End Of Packet

When set, indicates the last descriptor making up the packet. One or many

descriptors can be used to form a packet.

TDESC.CMD Description

321 0

RSV

TU

a

a. 82544GC/EI only.

LC EC DD