Software Developer’s Manual 225

Register Descriptions

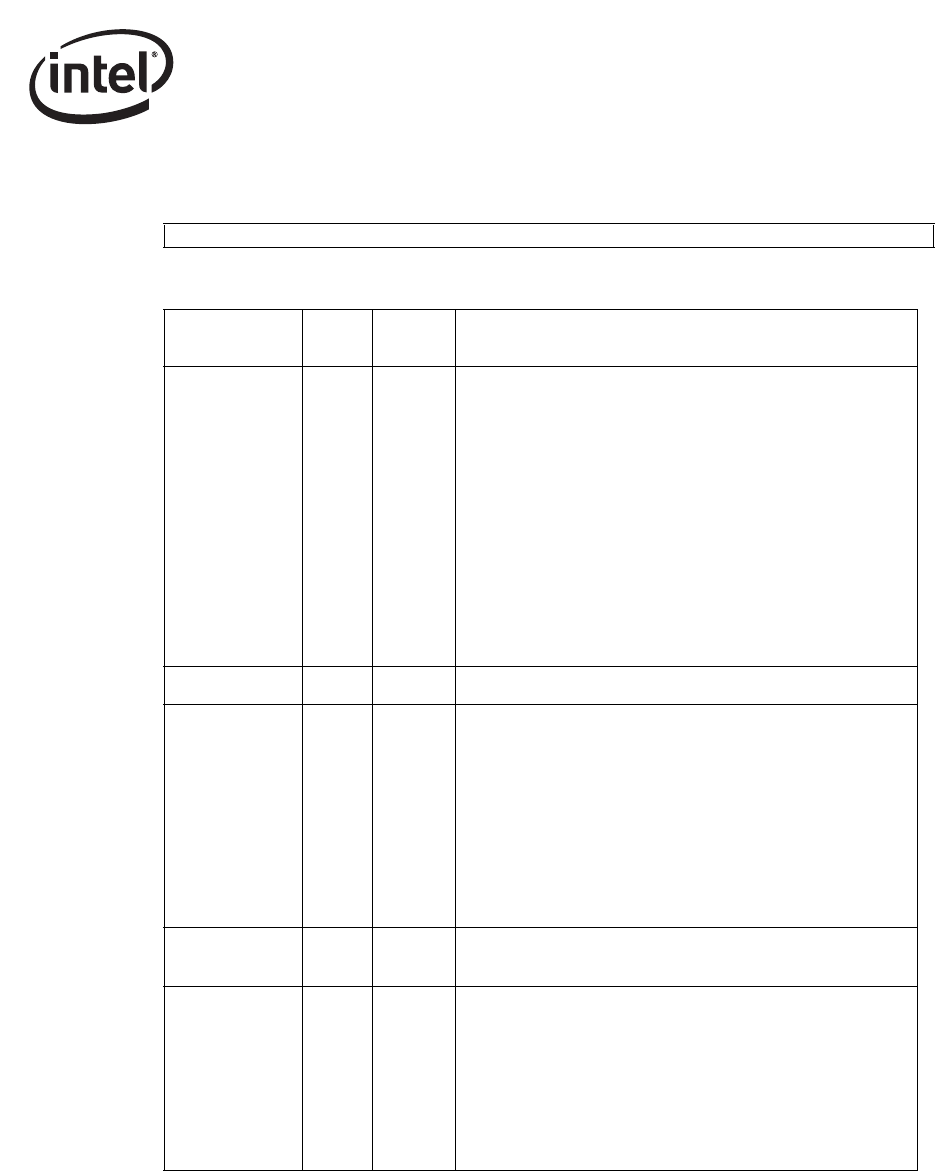

Table 13-3. CTRL Register Bit Description

31 0

Device Control Bits

Field Bit(s)

Initial

Value

Description

FD 0

1b

0b

1

Full-Duplex

Enables software to override the hardware Auto-Negotiation

function. The FD sets the duplex mode only if CTRL.FRCDPLX

is set.

When cleared, the Ethernet controller operates in half-duplex;

when set, the Ethernet controller operates in full-duplex.

When the Ethernet controller operates in TBI mode/internal

SerDes mode, and the AN Hardware is enabled, this bit is

ignored. When the Ethernet controller operates in TBI mode/

internal SerDes, and the AN Hardware is disabled, or the link is

forced, this bit should be set by software.

When the Ethernet controller operates in internal PHY mode,

the FD bit is set by software based on AN and data rate

resolution.

Configurable through the EEPROM.

Reserved 2:1 0b These bits are reserved and should be set to 00b.

LRST 3 1b

Link Reset (not applicable to the 82540EP/EM, 82541xx, or

82547GI/EI)

0b = Normal; 1b = Link Reset

Applicable only in TBI mode/internal SerDes of operation. Used

to reset the link control logic and restart the Auto-Negotiation

process, when TXCW.ANE is set and TBI mode/internal SerDes

is enabled.

When set, transmission and reception are halted regardless of

TBI mode/internal SerDes setting. A transition to 0b initiates the

Auto-Negotiation function. Configurable from the EEPROM,

allowing initiation of Auto-Negotiation function at power up.

Reserved 4 0b

Reserved

Factory use only. Should be written with 0b.

ASDE 5 0b

Auto-Speed Detection Enable.

When set, the Ethernet controller automatically detects the

resolved speed of the link by sampling the link in internal PHY

mode and self-configures the appropriate status and control

bits. Software must also set the SLU bit for this operation. This

function is ignored in TBI mode/internal Serdes. The ASD

feature provides a method of determining the link speed without

the need for software accesses to the MII management

registers.