308 Software Developer’s Manual

Register Descriptions

13.4.29 Receive Descriptor Tail

RDT (02818h;R/W)

This register contains the tail pointers for the receive descriptor buffer. The register points to a 16-

byte datum. Software writes the tail register to add receive descriptors to the hardware free list for

the ring.

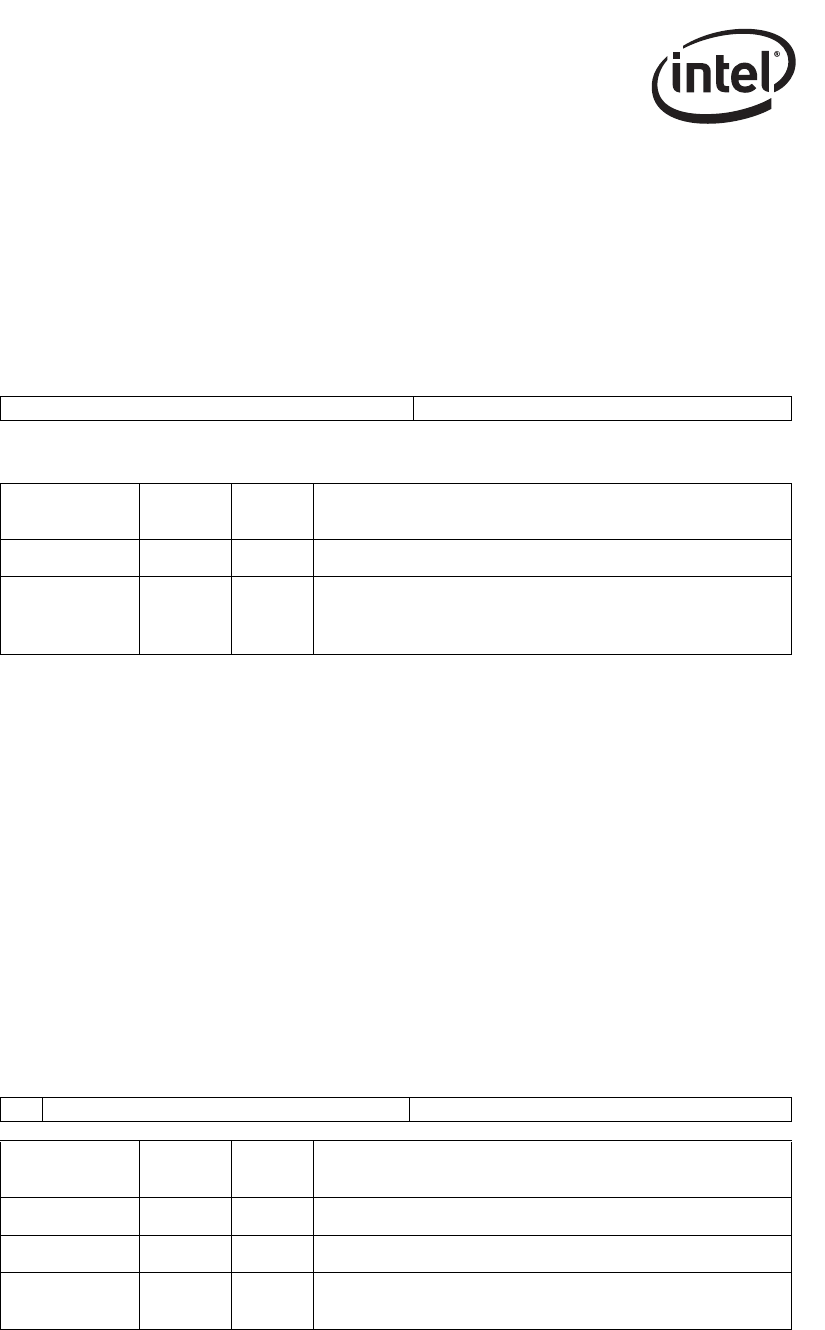

Table 13-74. RDT Register Bit Description

13.4.30 Receive Delay Timer Register

RDTR (02820h; R/W)

This register is used to delay interrupt notification for the receive descriptor ring. Delaying

interrupt notification helps maximize the number of receive packets serviced by a single interrupt.

Warning: It is strongly recommended that the Delay Timer field of this register not be used. For any

application requiring an interrupt moderation mechanism, it is recommended that the Interrupt

Throttling Register (ITR) be used instead. ITR provides a more direct interrupt solution than

RDTR. In addition, Intel software device drivers use ITR instead of RDTR. Refer to the

82546EB

Gigabit Ethernet Controller Specification Update or 82546GB Gigabit Ethernet Controller

Specification Update

for additional details.

Table 13-75. RDTR Register Bit Description

31 16 15 0

Reserved RDT

Field Bit(s)

Initial

Value

Description

RDT 15:0 0b Receive Descriptor Tail.

Reserved 31:16 0b

Reserved

Reads as 0b.

Should be written with 0b for future compatibility.

31 30 16 15 0

FPD Reserved Delay Timer

Field Bit(s)

Initial

Value

Description

Delay Timer 15:0 0b Receive delay timer measured in increments of 1.024 s.

Reserved 30:16 0b Reserved. Reads as 0b.

FPD 31 0b

Flush partial descriptor block when set to 1b; ignore otherwise.

Reads 0b (self-clearing).