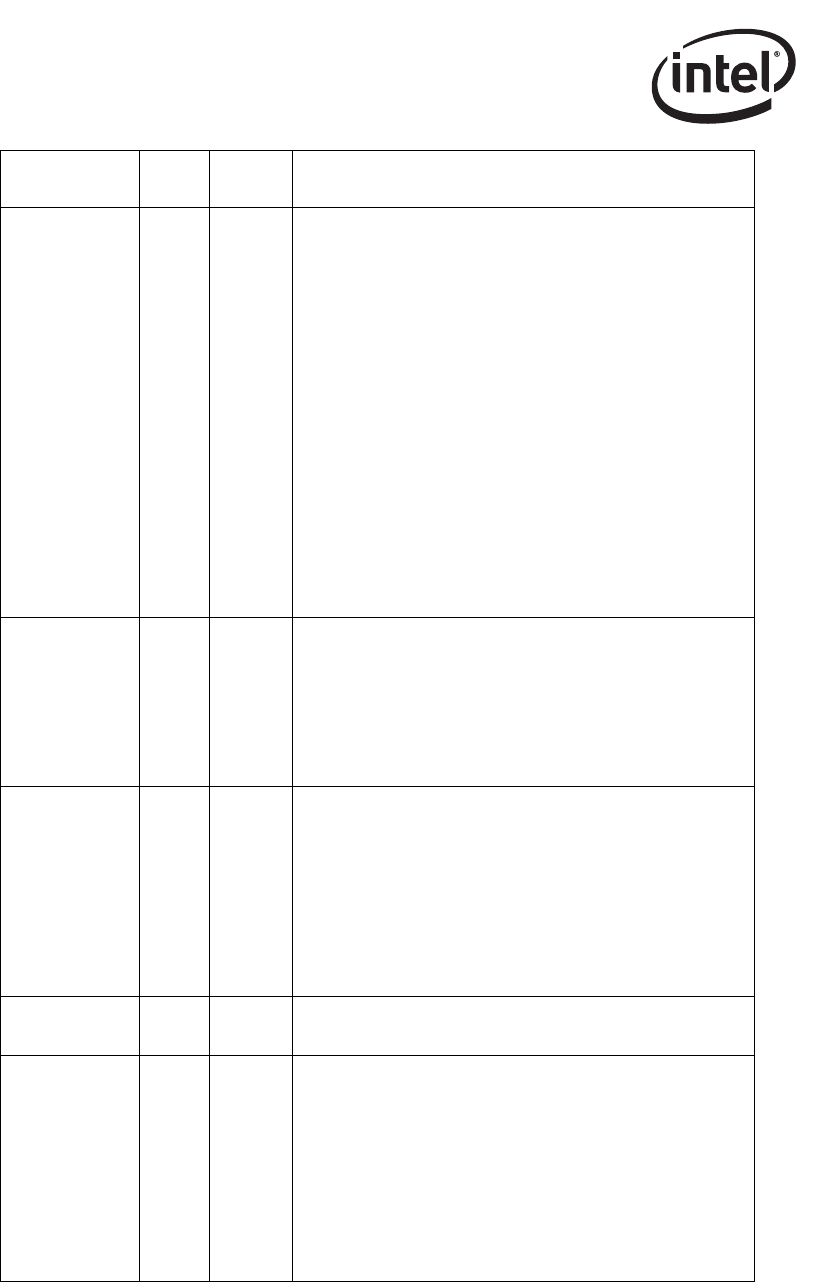

226 Software Developer’s Manual

Register Descriptions

SLU 6 0b

Set Link Up

In TBI mode/internal SerDes, provides manual link

configuration. When set, the Link Up signal is forced high once

receiver synchronization is achieved (LOS not asserted) using

CTRL.FD to determine the duplex mode. This operation

bypasses the link configuration process. If Auto-Negotiation is

enabled (TXCW.ANE equals 1b), then Set Link Up is ignored.

In internal PHY mode, this bit must be set to 1b to permit the

Ethernet controller to recognize the I_LOS/I_LIND link signal

from the PHY.

The "Set Link Up" is normally initialized to 0b. However, if either

the APM Enable or SMBus Enable bits are set in the EEPROM

then it is initialized to 1b, ensuring MAC/PHY communication

during preboot states (for example, the 82547EI and 82541EI).

Driver software sets this bit when the driver software initializes,

therefore LED indications (link, activity, speed) are not active

until the software driver loads even though the PHY has auto-

negotiated and established link with a partner on the Ethernet.

See Section 8.6 for more information about Auto-Negotiation

and link configuration in the various modes.

Configurable through the EEPROM.

ILOS 7 0b

Invert Loss-of-Signal (LOS).

0b = do not invert (active high input signal); 1b = invert signal

(active low input signal).

If using the internal PHY, this bit should be set to 0b to ensure

proper communication with the MAC. If using an external TBI

device, this bit can be set if the Ethernet controller provides a

link loss indication with negative polarity.

Note: This is a reserved bit for the 82541xx and 82547GI/EI.

SPEED 9:8 10b

Speed selection.

These bits determine the speed configuration and are written by

software after reading the PHY configuration through the MDI/O

interface. These signals are ignored in TBI mode/internal

Serdes or when Auto-Speed Detection (CTRL.ASDE) is

enabled. See Section 8.6 for details.

00b 10 Mb/s

01b 100 Mb/s

10b 1000 Mb/s

11b not used

Reserved 10 0b

Reserved

Should be written with 0b to ensure future compatibility.

FRCSPD 11 1b

Force Speed

When set, the Ethernet controller speed is configured by

CTRL.SPEED bits. The PHY device must resolve to the same

speed configuration or software must manually set it to the

same speed as the Ethernet controller.

When cleared, this allows the PHY device or ASD function

(CTRL.ASDE is set) to set the Ethernet controller speed.

This bit is superseded by the CTRL_EXT.SPD_BYPS bit, which

has a similar function.

Applicable only in internal PHY mode of operation and is

configurable through EEPROM.

Field Bit(s)

Initial

Value

Description