282 Software Developer’s Manual

Register Descriptions

13.4.7.1.26 MDI Register 30 Access Window

1

R30AW (30d; R/W)

13.4.7.1.27 Documented MDI Register 30 Operations

1

Unless otherwise specified, no reset operations are required in order for the following operations to

take effect.

NOTE: Any time the PHY is reset it returns to Class AB drive mode.

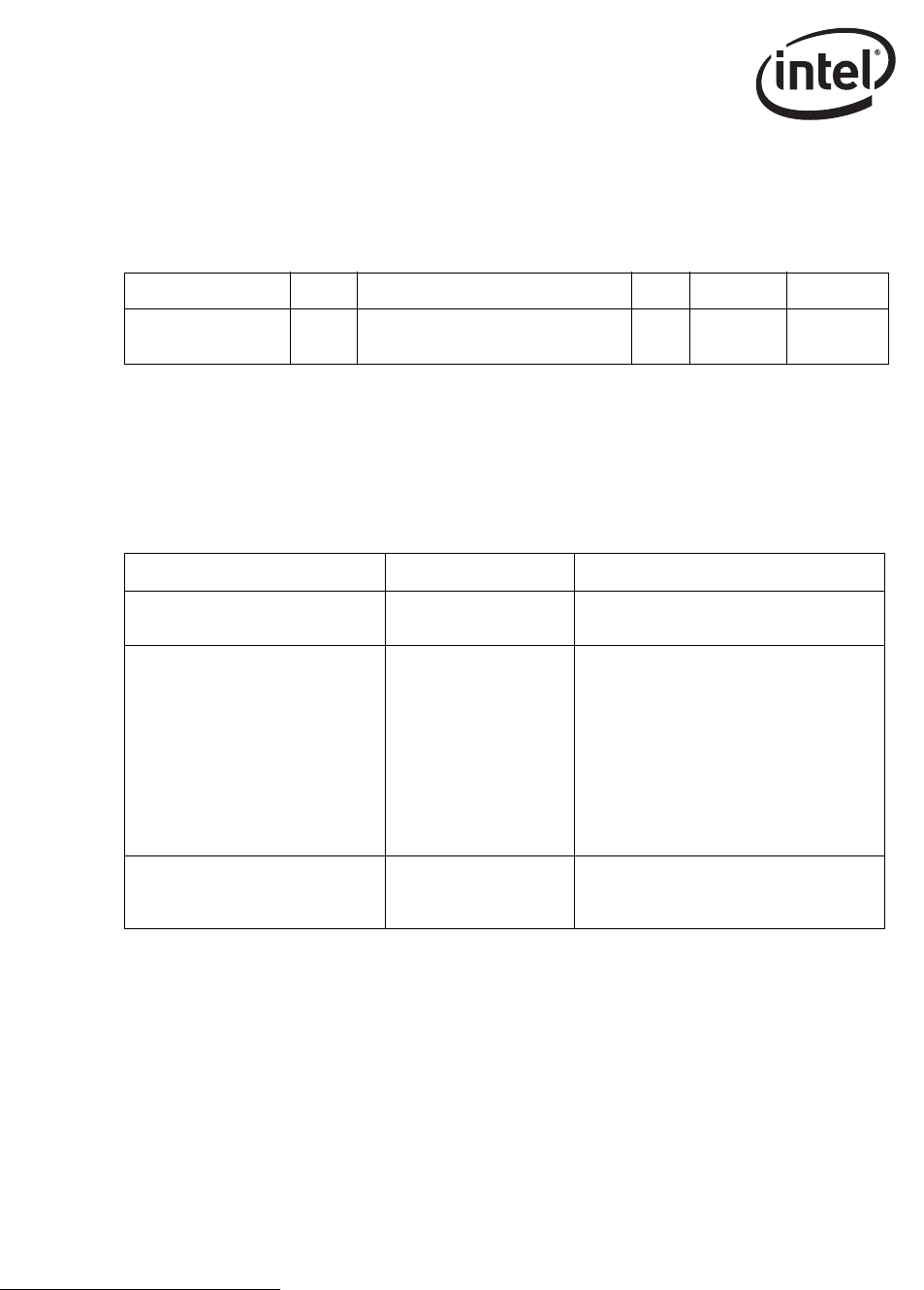

Table 13-50. MDI Register 30 Page Select Bit Description

Field Bit(s) Description Mode HW Rst SW Rst

Register 30 Access 15:0

Provides read/write capability for

register selected via MDI register 29.

R/W 0000h 0000h

1. Not applicable to the 82544GC/EI, 82541xx, or 82547GI/EI.

Table 13-51. MDI Register 30 Operations

To Perform Operation MDI Read/Write Sequence

Power down SerDes (optimize

power for copper PHY operation)

1

1. Not applicable to 82540EP/EM

30_31.15:0 <= x2001h

• Write MDI register 29 <= 31d

• Write MDI register 30 <= 2001h

Tune VCO on SerDes Rx for

optimal Bit Error Ratio (BER)

1

30_5.8 <= 0b

30_4.11 <= 1b

• Write MDI register 29 <= 5d

• Read MDI register 30

• Change bit 8 to 0

• Write result to MDI register 30

• Write MDI register 29 <= 4d

• Read MDI register 30

• Change bit 11 to 1

• Write result to MDI register 30

Set PHY output drivers into Class A

mode (Class AB is default after

reset)

30_11.15:0 = 8004h

• Write MDI register 29 = 11d

• Write MDI register 30 = 8004h