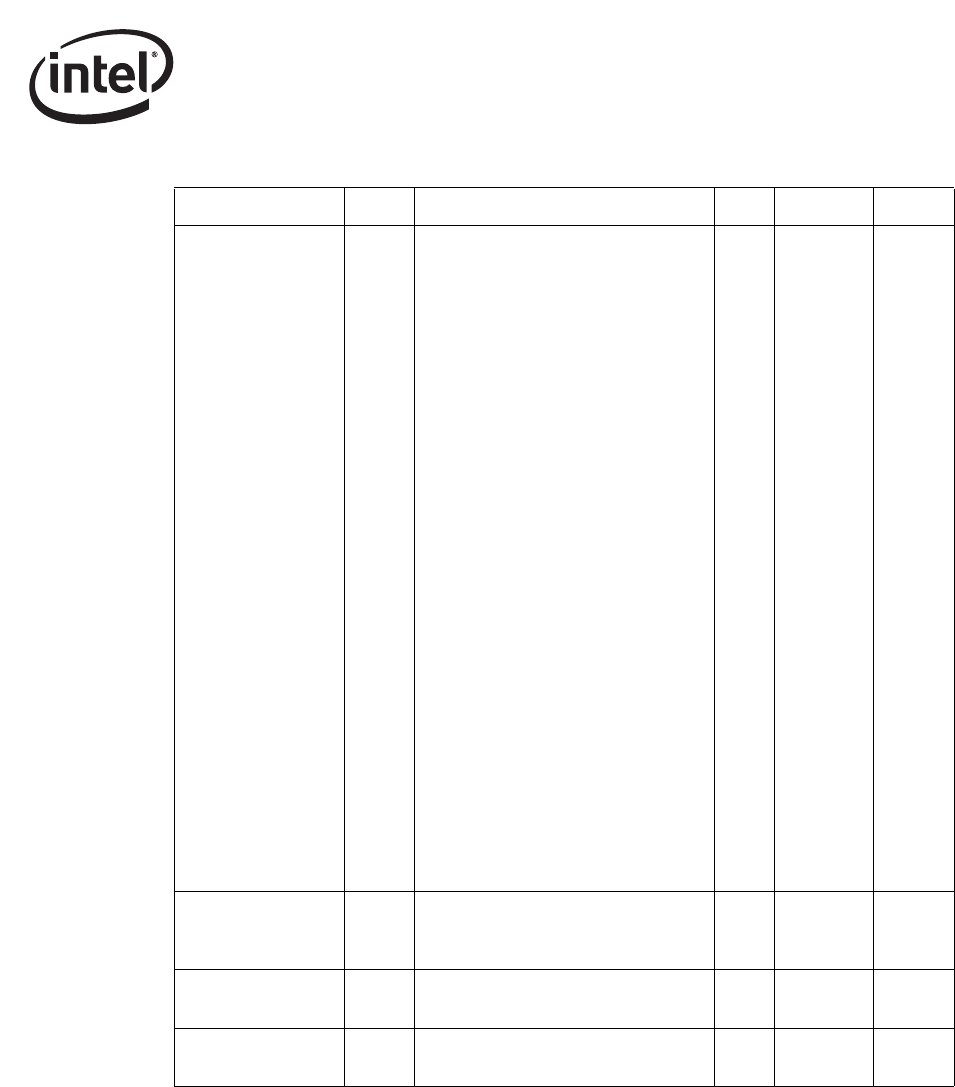

Software Developer’s Manual 247

Register Descriptions

Auto-Negotiation

Enable

12

1b = Enable Auto-Negotiation Process.

0b = Disable Auto-Negotiation Process.

A write to this bit does not take effect

until a software reset is asserted,

Restart Auto-Negotiation is asserted, or

Power Down transitions from power

down to normal operation.

When the port is switched from power

down to normal operation, software

reset and restart Auto-Negotiation are

performed even if bits Reset and Restart

Auto-Negotiation are not set by the

programmer.

If bit 12 is set to 0b and speed is

manually forced to 1000 Mbps in bits 13

and 6, then Auto-Negotiation is still

enabled and only 1000BASE-T full

duplex is advertised if bit 8 is set to 1b.

1000BASE-T half duplex is advertised if

bit 8 is cleared (0b). Duplex settings in

other registers are ignored. Auto-

Negotiation is required by IEEE for

proper operation in 1000BASE-T.

82544GC/EI only:

Auto-Negotiation enable takes on the

value set by external pins ANEG[3:0] on

hardware reset only.

Bit 12: ANEG[3:2] = 11b.

If MODE[3:0] equals 001xb or 0111b,

where x equals either 0b or 1b, then the

ANE bit determines whether

1000BASE-X Auto-Negotiation is on or

off. Otherwise ANE determines whether

10/100/1000BASE-T Auto-Negotiation

is on or off.

R/W

R/W

1b

ANEG[3:2]

ENA_XC

Update

Update

Speed Selection

(LSB)

13 See Speed Selection (MSB), bit 6.

R/W 0b

ANEG[3:1]

2

MODE[3:0]

Update

Loopback 14

1b = Enable loopback.

0b = Disable loopback.

R/W 0b 0b

Reset 15

1b = PHY reset.

0b = Normal operation.

R/W,

SC

0b

Self

Clear

1. 82541xx and 82547GI/EI only.

2. 82544GC/EI only.

Table 13-16. PHY Control Register Bit Description

Field Bit(s) Description Mode HW Rst SW Rst