Software Developer’s Manual 89

PCI Local Bus Interface

4.3.1.2 MW Bursts

•

The Ethernet controller always continues the burst until the end. If the system is concerned

about MWI usage, it disconnects at the cache line boundary. The Ethernet controller then

restarts the transaction and re-evaluates command usage.

Note: The algorithm described above defaults to the MW case when the MWI enable bit in the

Configuration Register is set to 0b.

4.3.2 Memory Read Operations

For all read commands, the hardware evaluates the amount of data to be read with respect to the

cache line size register and the read address alignment for command determination. The following

rules apply:

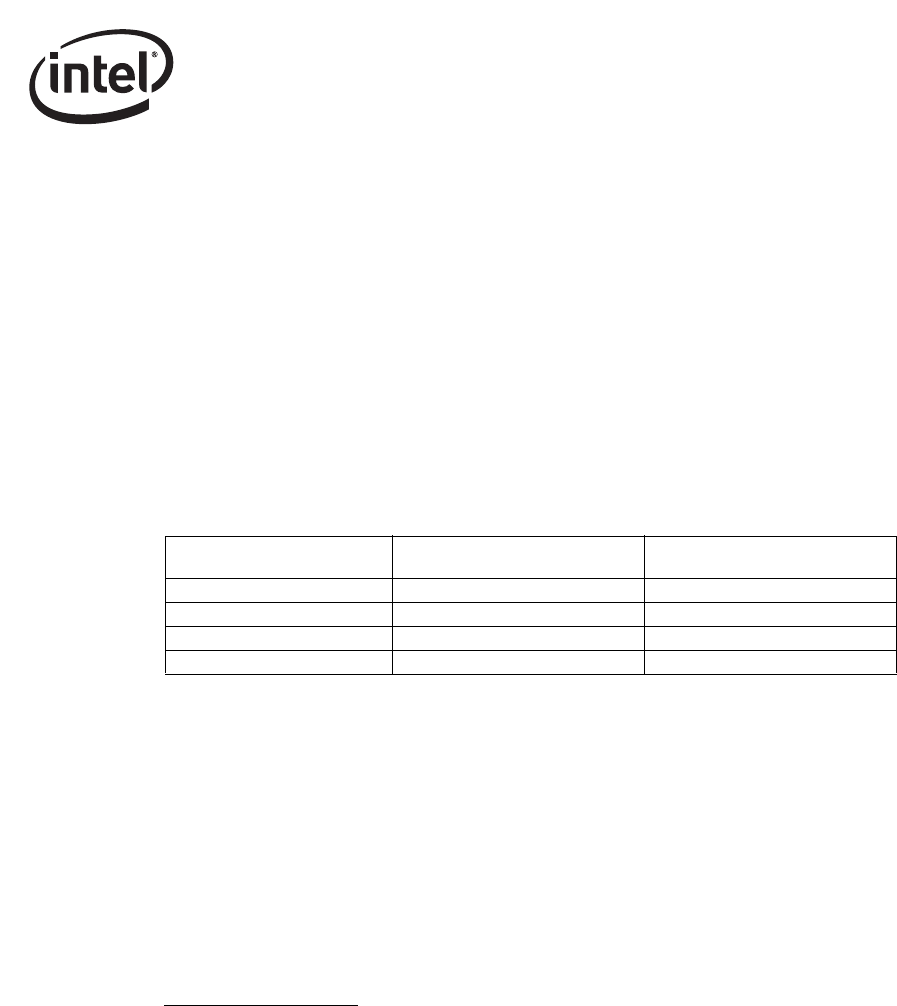

Table 4-8. Rules for Memory Read Operations

In other words, read command usage depends on the number of cache lines from which the data

must be read from the target device.

As mentioned above, unsupported values in the cache line size field default to a size of 32 bytes for

the memory read command usage algorithm.

Note: MRL should be used for a single cache line of data that is cache line aligned.

4.3.2.1 PCI-X Command Usage

In PCI-X mode, the Ethernet controller takes advantage of split transaction protocol to minimize

retries and eliminate delayed read transactions.

Target Split Responses

When the Ethernet controller responds to a Memory Read or I/O Read command it determines if

the data can be returned within 16 clock cycles. If not, it signals a split response and returns data

later through the split completion protocol. If the Ethernet controller already has a command in its

completion register it retries the requested read until the register is empty. Target posted writes and

split completion are still accepted during that period. The internal register reads that cause splits

are:

• General Registers: CTRL, STATUS, EECD, CTRL_EXT, FCAL, FCAH, FCT, VET, FCTTV,

TXCW, RXCW, PBA,

• Interrupt Registers: ICR, ICS, IMS, IMC

• Transmit Registers: TCTL

Amount of

Data Requested

Number of Cache Line

Boundaries Crossed

Command

Used by Hardware

> 2 Cache Lines n/a MRM

>= 1 Cache Line >= 2 MRM

<= 1 Cache Line 0 or 1 MRL

< 1 Cache Line 0 MR