Software Developer’s Manual 325

Register Descriptions

13.4.47 Receive Checksum Control

RXCSUM (05000h; R/W)

The Receive Checksum Control register controls the receive checksum offloading features of the

Ethernet controller. The Ethernet controller supports the offloading of three receive checksum

calculations: the Packet Checksum, the IP Header Checksum, and the TCP/UDP Checksum.

The frame types that are supported:

• Ethernet II

• Ethernet SNAP

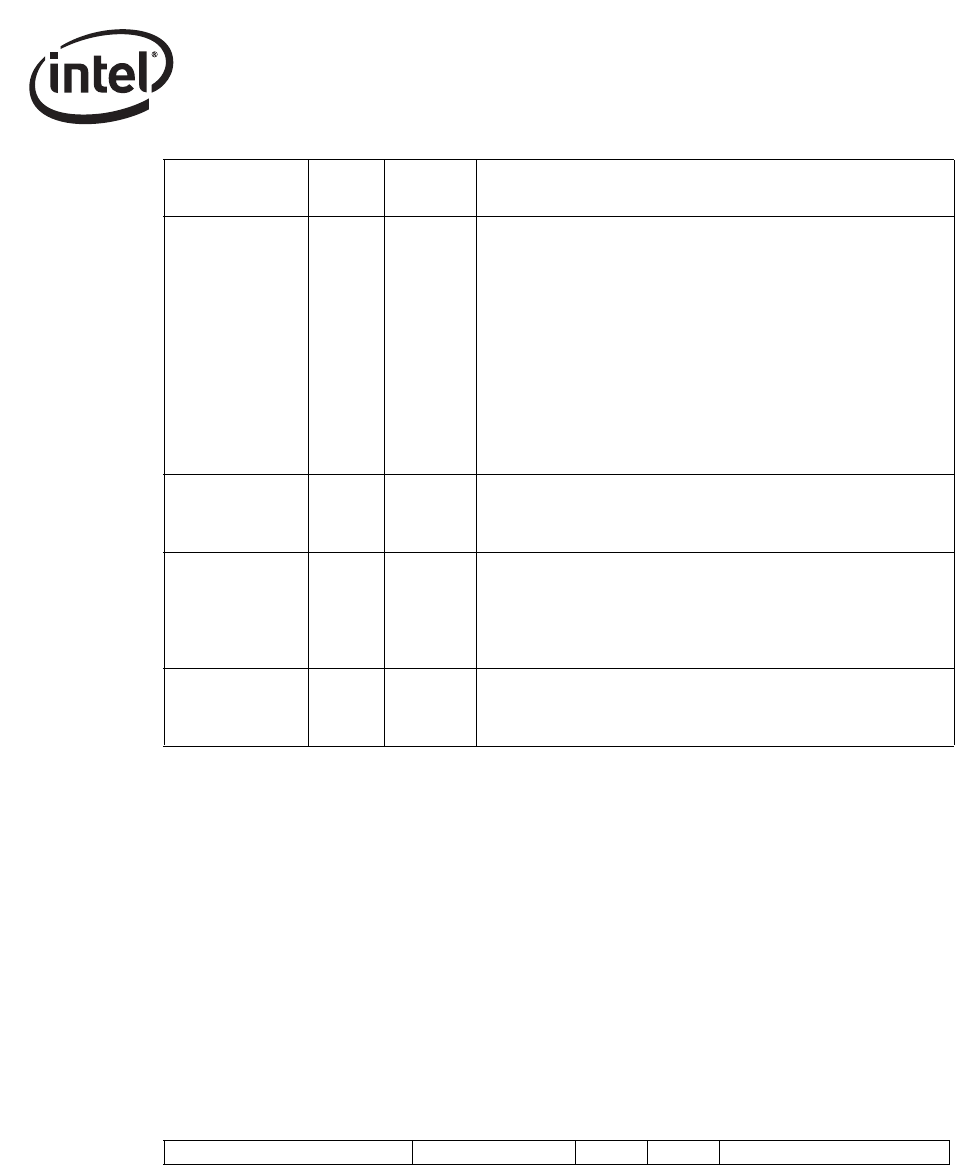

Table 13-88. RXCSUM Register Bit Description

WTHRESH 21:16 1b

Write Back Threshold

WTHRESH controls the write back of processed receive

descriptors. This threshold refers to the number of receive

descriptors in the Ethernet controller’s on-chip buffer which are

ready to be written back to host memory. In the absence of

external events (explicit flushes), the write back occurs only after

more than WTHRESH descriptors are available for write back.

WTHRESH must contain a non-zero value to take advantage of

the write back bursting capabilities of the Ethernet controller.

A value of 1b causes the descriptors to be written back as soon

as one cache line is available. A value of WTHRESH can be in

either cache line units, or based on number of descriptors based

on RXDCTL.GRAN.

RSV 23:22 0b

Reserved

Reads as 0b.

Should be written as 0b for future compatibility.

GRAN 24 1b

Granularity

Set the values of PTHRESH, HTHRESH and WTHRESH in units

of cache lines or descriptors (each descriptor is 16 bytes)

0b = Cache line granularity.

1b = Descriptor granularity.

Reserved 31:25 0b

Reserved

Reads as 0b.

Should be written as 0b for future compatibility.

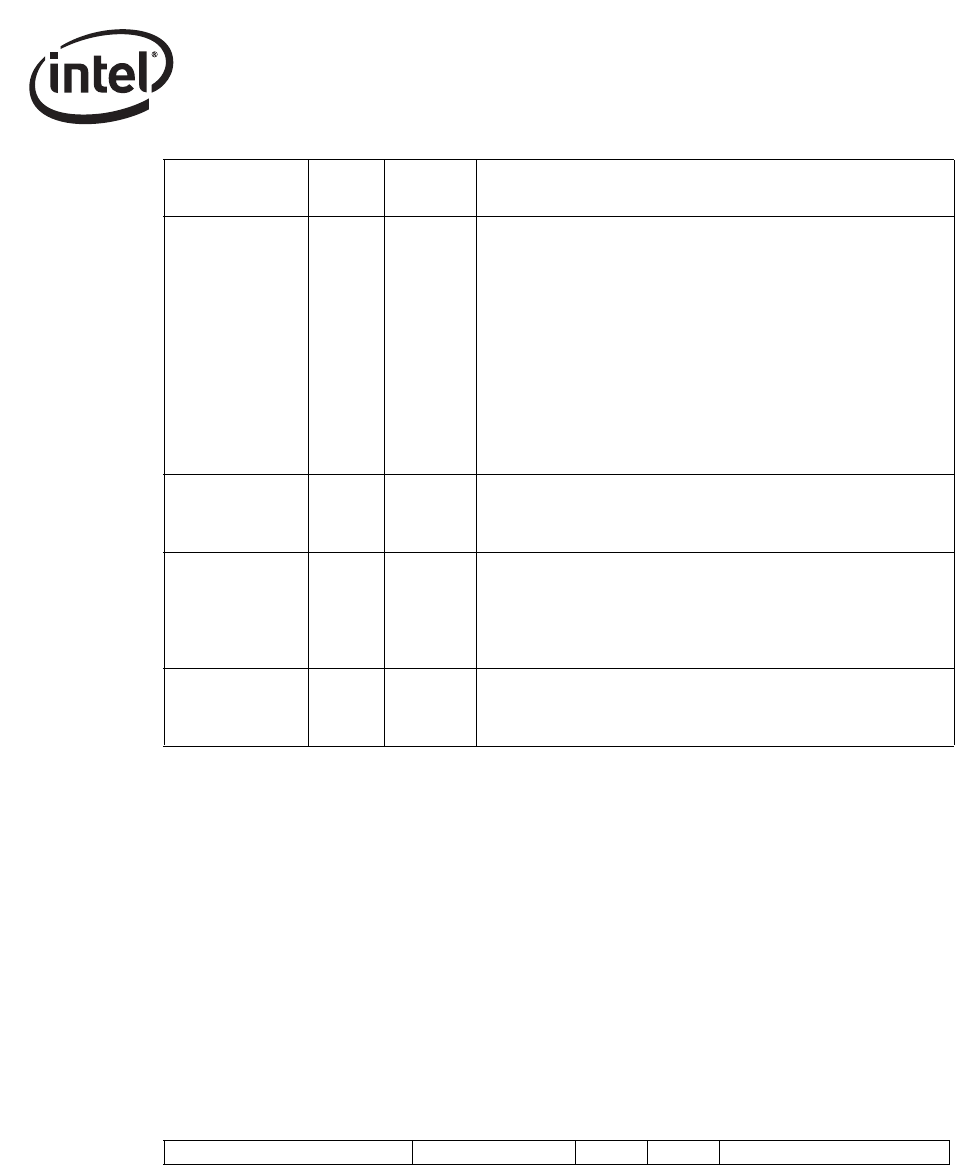

Field Bit(s)

Initial

Value

Description

31:11 10 9 8 7 0

RSV IPV6OFL

1

1. Not applicable to the 82544GC/EI.

TUOFLD IPOFLD PCSS