296 Software Developer’s Manual

Register Descriptions

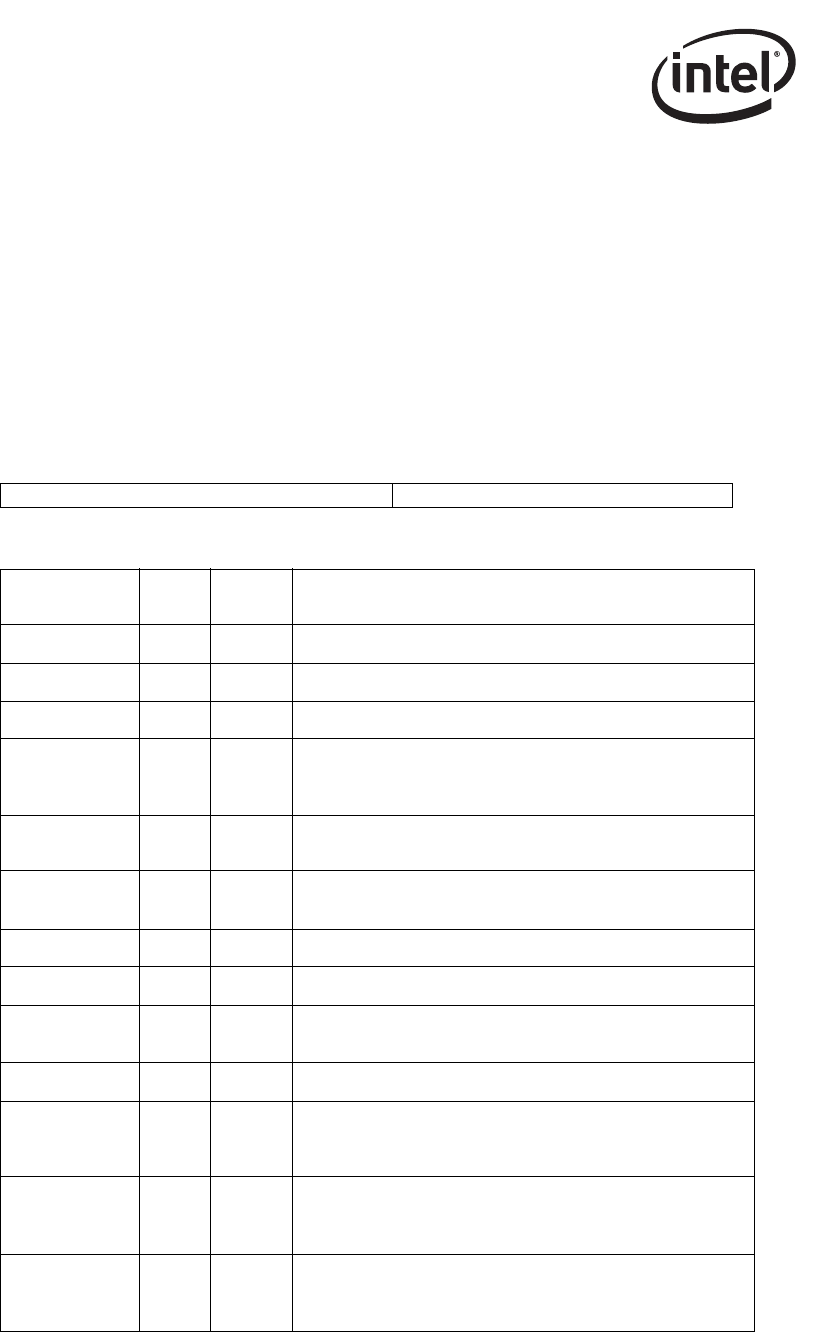

13.4.19 Interrupt Cause Set Register

ICS (000C8h; W)

Software uses this register to set an interrupt condition. Any bit written with a 1b sets the

corresponding interrupt. This results in the corresponding bit being set in the Interrupt Cause Read

Register (see Section 13.4.17). A PCI interrupt is generated if one of the bits in this register is set

and the corresponding interrupt is enabled through the Interrupt Mask Set/Read Register (see

Section 13.4.20).

Bits written with 0b are unchanged.

Table 13-64. ICS Register Bit Description

31 17 16 0

Reserved ICS Bits

Field Bit(s)

Initial

Value

Description

TXDW 0 X Sets Transmit Descriptor Written Back Interrupt.

TXQE 1 X Sets Transmit Queue Empty Interrupt.

LSC 2 X Sets Link Status Change Interrupt.

RXSEQ 3 X

Sets Receive Sequence Error Interrupt.

This is a reserved bit for the 82541xx and 82547GI/EI. Set to

0b.

RXDMT0 4 X

Sets Receive Descriptor Minimum Threshold Reached

Interrupt.

Reserved 5 X

Reserved

Should be written with 0b to ensure future compatibility.

RXO 6 X Sets on Receiver FIFO Overrun Interrupt.

RXT0 7 X Sets Receiver Timer Interrupt.

Reserved 8 X

Reserved

Should be written with 0b to ensure future compatibility.

MDAC 9 X Sets MDI/O Access Complete Interrupt.

RXCFG 10 X

Sets Receiving /C/ ordered sets Interrupt.

This is a reserved bit for the 82541xx and 82547GI/EI. Set to

0b.

Reserved 11 X

Reserved

Should be written with 0b to ensure future compatibility.

Not applicable to the 82544GC/EI.

PHYINT 12 X

Sets PHY interrupt. Not applicable to the 82544GC/EI.

This is a reserved bit for the 82541xx and 82547GI/EI. Set to

0b.