GD82559ER — Networkin

g

Silicon

18

Datasheet

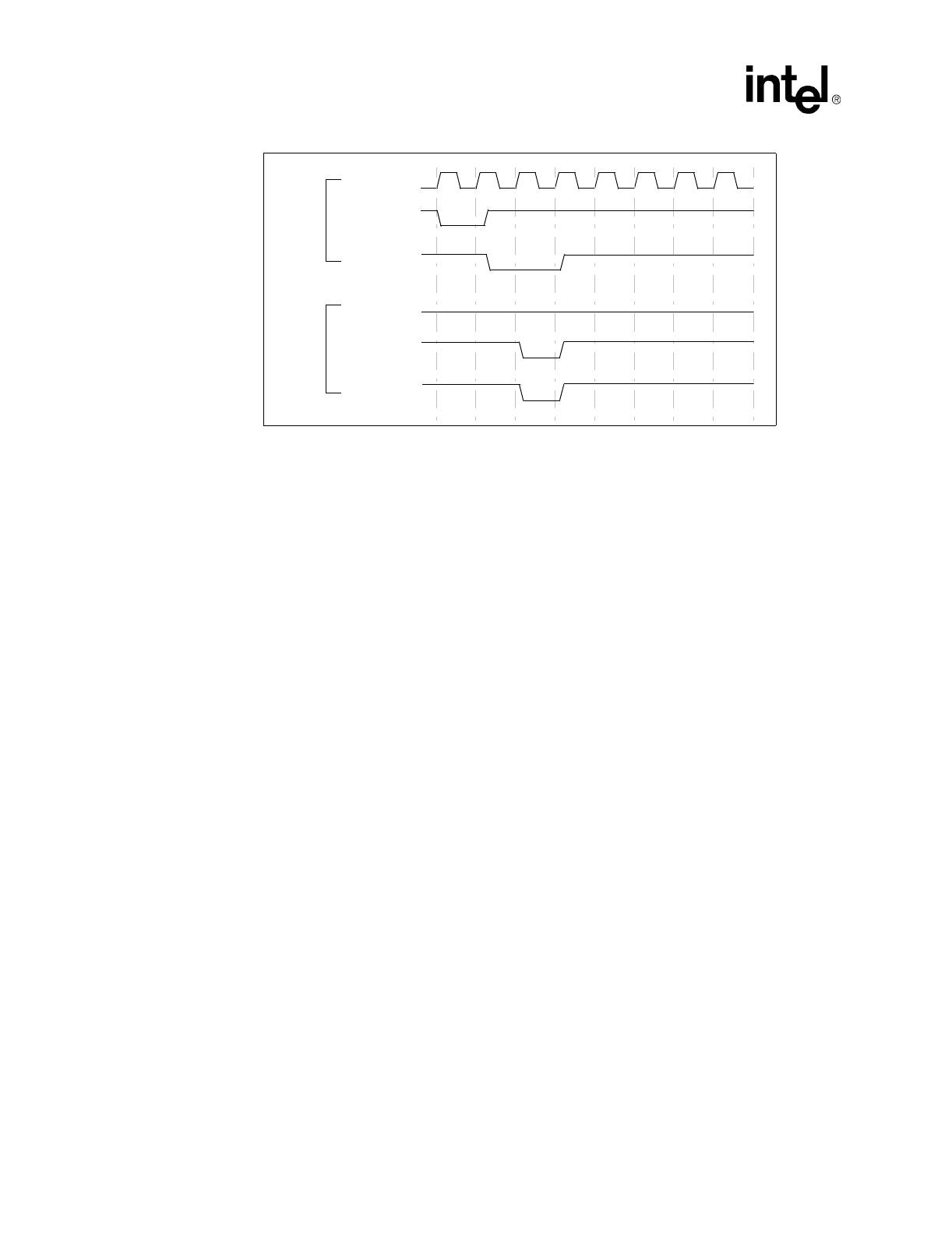

Note:

The 82559ER is considered the target in the above diagram; thus, TRDY# is not asserted.

4.2.1.1.4 Error Handlin

g

Data Parity Errors:

The 82559ER checks for data parity errors while it is the target of the

transaction. If an error was detected, the 82559ER always sets the Detected Parity Error bit in the

PCI Configuration Status register, bit 15. The 82559ER also asserts PERR#, if the Parity Error

Response bit is set (PCI Configuration Command register, bit 6). The 82559ER does not attempt to

terminate a cycle in which a parity error was detected. This gives the initiator the option of

recovery.

Target-Disconnect:

The 82559ER prematurely terminate a cycle in the following cases:

•

After accesses to the Flash buffer

•

After accesses to its CSR

•

After accesses to the configuration space

System Error:

The 82559ER reports parity error during the address phase using the SERR# pin. If

the SERR# Enable bit in the PCI Configuration Command register or the Parity Error Response bit

are not set, the 82559ER only sets the Detected Parity Error bit (PCI Configuration Status register,

bit 15). If SERR# Enable and Parity Error Response bits are both set, the 82559ER sets the

Signaled System Error bit (PCI Configuration Status register, bit 14) as well as the Detected Parity

Error bit and asserts SERR# for one clock.

The 82559ER, when detecting system error, will claim the cycle if it was the target of the

transaction and continue the transaction as if the address was correct.

Note:

The 82559ER will report a system error for any parity error during an address phase, whether or

not it is involved in the current transaction.

4.2.1.2 82559ER Bus Master O

p

eration

As a PCI Bus Master, the 82559ER initiates memory cycles to fetch data for transmission or

deposit received data and for accessing the memory resident control structures. The 82559ER

performs zero wait state

burst read and write cycles to the host main memory. Figure 7 and Figure

Fi

g

ure 6. PCI Retr

y

C

y

cle

SYSTEM

82559ER

CLK

FRAME#

IRDY#

TRDY#

DEVSEL#

STOP#