GD82559ER — Networkin

g

Silicon

52

Datasheet

Note:

Bit 0 in all base registers is read only and used to determine whether the register maps into memory

or I/O space. Base registers that map to memory space must return a 0b in bit 0. Base registers that

map to I/O space must return 1b in bit 0.

Base registers that map into I/O space are always 32 bits wide with bit 0 hardwired to a 1b, bit 1 is

reserved and must return 0b on reads, and the other bits are used to map the device into I/O space.

The number of upper bits that a device actually implements depends on how much of the address

space the device will respond to. For example, a device that wants a 1 Mbyte memory address

space would set the most significant 12 bits of the base address register to be configurable, setting

the other bits to 0b.

The 82559ER contains BARs for the Control/Status Register (CSR), Flash, and Expansion ROM.

7.1.9.1 CSR Memor

y

Ma

pp

ed Base Address Re

g

ister

The 82559ER requires one BAR for memory mapping. Software determines which BAR, memory

or I/O, is used to access the 82559ER CSR registers.

The memory space for the 82559ER CSR Memory Mapped BAR is 4 Kbyte. It is marked as

prefetchable space and is mapped anywhere in the 32-bit memory address space.

7.1.9.2 CSR I/O Ma

pp

ed Base Address Re

g

ister

The 82559ER requires one BAR for I/O mapping. Software determines which BAR, memory or

I.O, is used to access the 82559ER CSR registers. The I/O space for the 82559ER CSR I/O BAR is

64 bytes.

7.1.9.3 Flash Memor

y

Ma

pp

ed Base Address Re

g

ister

The Flash Memory BAR is a Dword register. The 82559ER physically supports up to a 128 Kbyte

Flash device, and requests a 128Kbyte window. The 82559ER always claims a Flash memory

window, regardless of whether or not a Flash device is connected (i.e. Flash Base Address Register

cannot be disabled).

7.1.9.4 Ex

p

ansion ROM Base Address Re

g

ister

The Expansion ROM BAR is a Dword register and supports a 128 Kbyte memory via the 82559ER

local bus. The Expansion ROM BAR can be disabled by setting the Boot Disable bit of the

EEPROM (word AH, bit 11). The 82559ER requests a 1MB window for expansion ROM. If the

Boot Disable bit is set, the 82559ER returns a 0b for all bits in this address register, avoiding

request of memory allocation for this space.

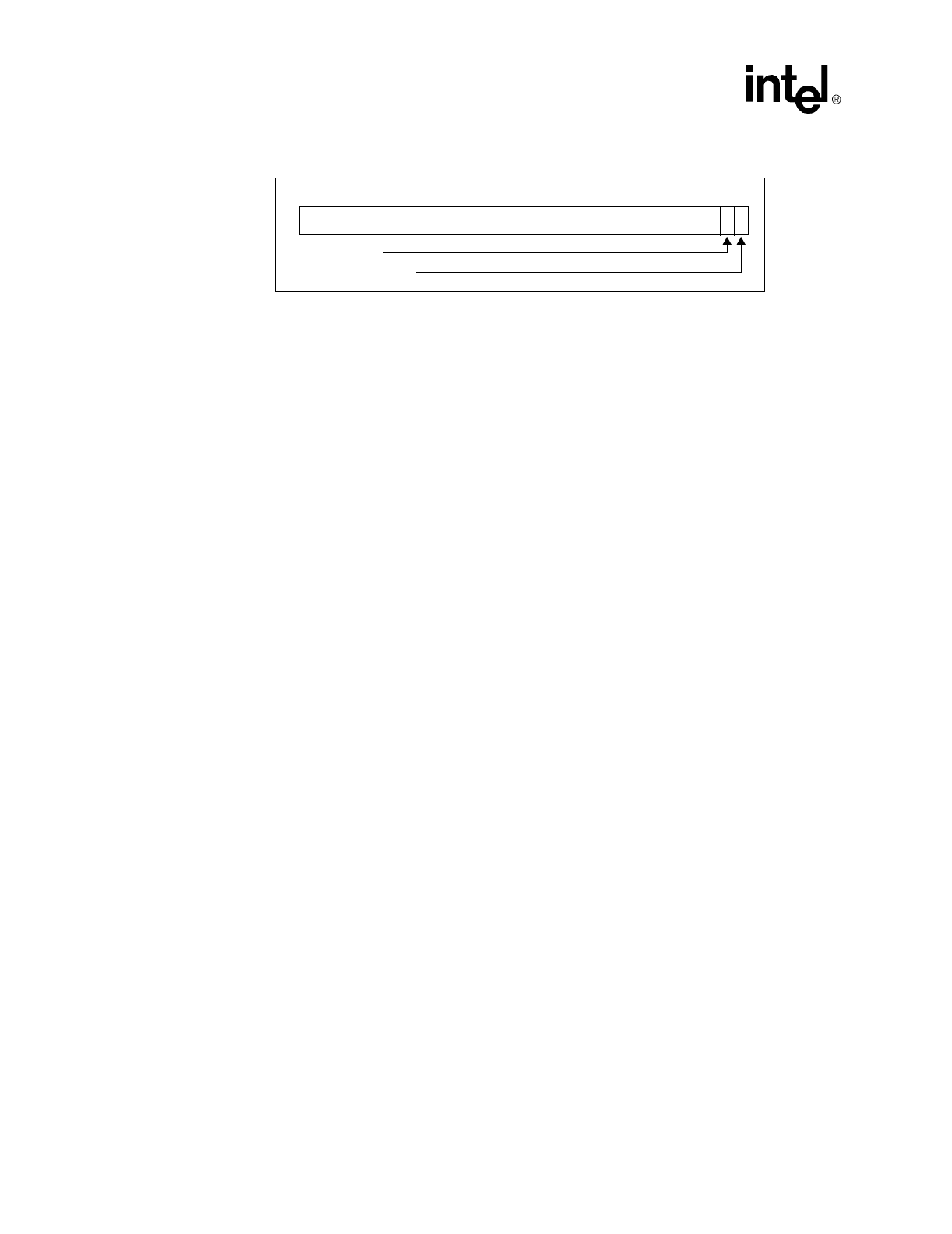

Fi

g

ure 22. Base Address Re

g

ister for I/O Ma

pp

in

g

Base Address

0

0

31

21

Reserved

I/O space indicator

1