Datasheet

47

Networkin

g

Silicon — GD82559ER

7. PCI Confi

g

uration Re

g

isters

The 82559ER acts as both a master and a slave on the PCI bus. As a master, the 82559ER interacts

with the system main memory to access data for transmission or deposit received data. As a slave,

some 82559ER control structures are accessed by the host CPU to read or write information to the

on-chip registers. The CPU also provides the 82559ER with the necessary commands and pointers

that allow it to process receive and transmit data.

7.1 LAN

(

Ethernet

)

PCI Confi

g

uration S

p

ace

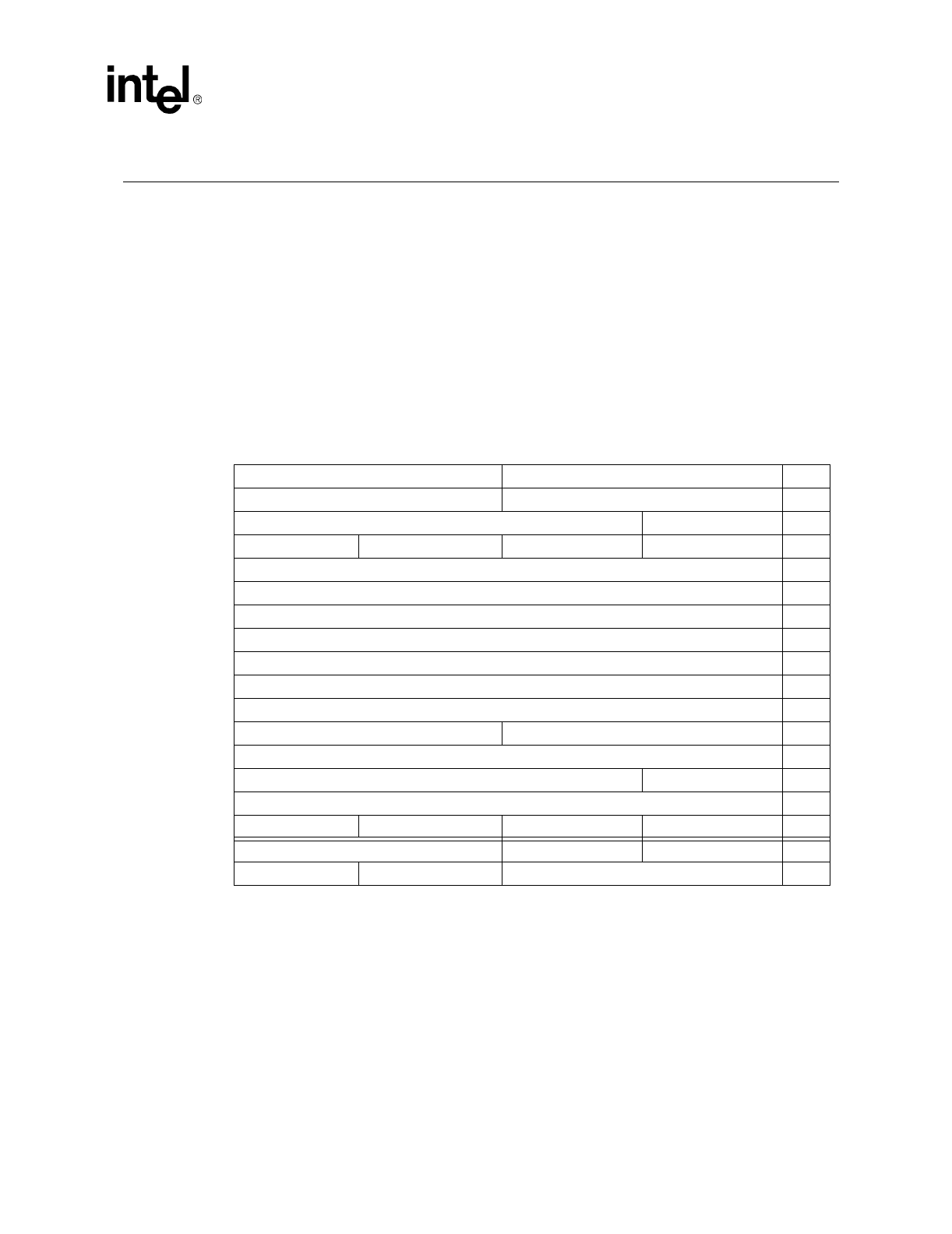

The 82559ER PCI configuration space is configured as 16 Dwords of Type 0 Configuration Space

Header, as defined in the PCI Specification, Revision 2.1. A small section is also configured

according to its device specific configuration space. The configuration space header is depicted

below in Figure 17.

7.1.1 PCI Vendor ID and Device ID Re

g

isters

The Vendor ID and Device ID of the 82559ER are both read only word entities. Their HARD-

CODED values are:

Vendor ID: 8086H

Device ID: 1209H

Device ID Vendor ID 00H

Status Command 04H

Class Code Revision ID 08H

BIST Header T

y

pe Latenc

y

Timer Cache Line Size 0CH

CSR Memor

y

Mapped Base Address Re

g

ister 10H

CSR I/O Mapped Base Address Re

g

ister 14H

Flash Memor

y

Mapped Base Address Re

g

ister 18H

Reserved Base Address Re

g

ister 1CH

Reserved Base Address Re

g

ister 20H

Reserved Base Address Re

g

ister 24H

Reserved 28H

Subs

y

stem ID Subs

y

stem Vendor ID 2CH

Expansion ROM Base Address Re

g

ister 30H

Reserved Cap_Ptr 34H

Reserved 38H

Max_Lat Min_Gnt Interrupt Pin Interrupt Line 3CH

Power Mana

g

ement Capabilities Next Item Ptr Capabilit

y

ID DCH

Reserved Data Power Mana

g

ement CSR E0H

Fi

g

ure 17. PCI Confi

g

uration Re

g

isters