Datasheet

49

Networkin

g

Silicon — GD82559ER

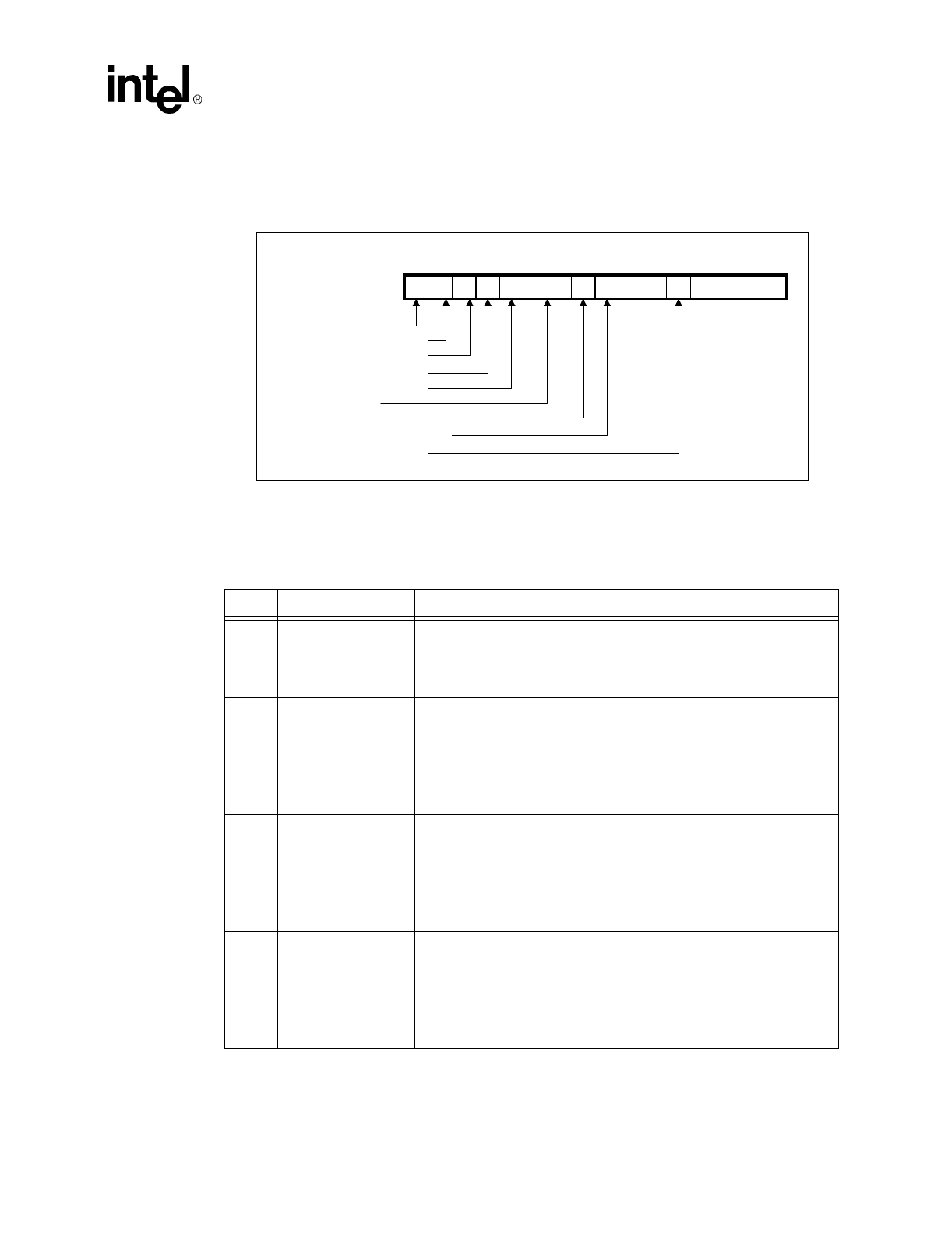

7.1.3 PCI Status Register

The 82559ER Status register is used to record status information for PCI bus related events. The

format of this register is shown in the figure below.

Note that bits 21, 22, 26, and 27 are set to 0b and bits 20, 23, and 25 are set to 1b. The PCI Status

register bits are described in the table below.

Fi

g

ure 19. PCI Status Re

g

ister

0

Detected Parit

y

Error

Si

g

naled S

y

stem Error

Received Master Abort

Received Tar

g

et Abort

Si

g

naled Tar

g

et Abort

Devsel Timin

g

Parit

y

Error Detected

Fast Back To Back

(

tar

g

et

)

Capabilities List

Reserved011000 10

31 30 29 28 27 26 25 24 23 22 21 20 19 16

Table 6. PCI Status Re

g

ister Bits

Bits Name Description

31 Detected Parit

y

Error

This bit indicates whether a parit

y

error is detected. This bit must be

asserted b

y

the device when it detects a parit

y

error, even if parit

y

error

handlin

g

is disabled

(

as controlled b

y

the Parit

y

Error Response bit in the

PCI Command re

g

ister, bit 6

)

. In the 82559ER, the initial value of the

Detected Parit

y

Error bit is 0b. This bit is set until cleared b

y

writin

g

a 1b.

30 Si

g

naled S

y

stem Error

This bit indicates when the device has asserted SERR#. In the 82559ER,

the initial value of the Si

g

naled S

y

stem Error bit is 0b. This bit is set until

cleared b

y

writin

g

a 1b.

29

Received Master

Abort

This bit indicates whether or not a master abort has occurred. This bit must

be set b

y

the master device when its transaction is terminated with a

master abort. In the 82559ER, the initial value of the Received Master

Abort bit is 0b. This bit is set until cleared b

y

writin

g

a 1b.

28 Received Tar

g

et Abort

This bit indicates that the master has received the tar

g

et abort. This bit

must be set b

y

the master device when its transaction is terminated b

y

a

tar

g

et abort. In the 82559ER, the initial value of the Received Tar

g

et Abort

bit is 0b. This bit is set until cleared b

y

writin

g

a 1b.

27 Si

g

naled Tar

g

et Abort

This bit indicates whether a transaction was terminated b

y

a tar

g

et abort.

This bit must be set b

y

the tar

g

et device when it terminates a transaction

with tar

g

et abort. In the 82559ER, this bit is alwa

y

s set to 0b.

26:25 DEVSEL# Timin

g

These two bits indicate the timin

g

of DEVSEL#:

00b - Fast

01b - Medium

10b - Slow

11b - Reserved

In the 82559ER, these bits are alwa

y

s set to 01b, medium.